with 4nm, 3nm, 20A and 18A?!

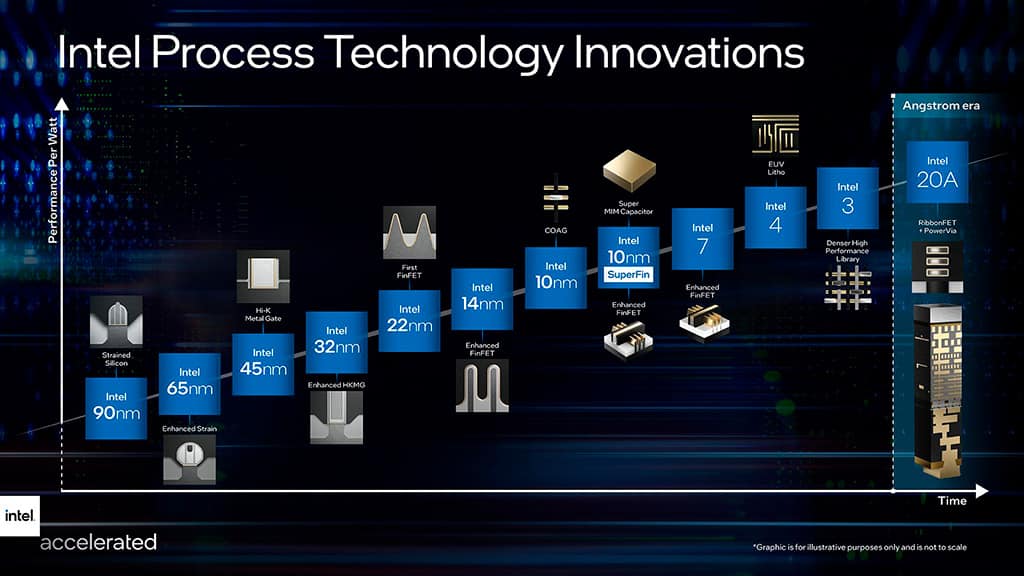

In today’s Intel Accelerated event, the company is driving a stake into the ground regarding where it wants to be by 2025. CEO Pat Gelsinger earlier this year stated that Intel would be returning to product leadership in 2025, but hasn’t yet explained how this is coming about – that is until today, where Intel has disclosed its roadmap for its next five generations of process node technology leading to 2025. Intel believes it can follow an aggressive strategy to match and pass its foundry rivals, while at the same time developing new packaging offerings and starting a foundry business for external customers. On top of all this, Intel has renamed its process nodes.

The Short Answer:

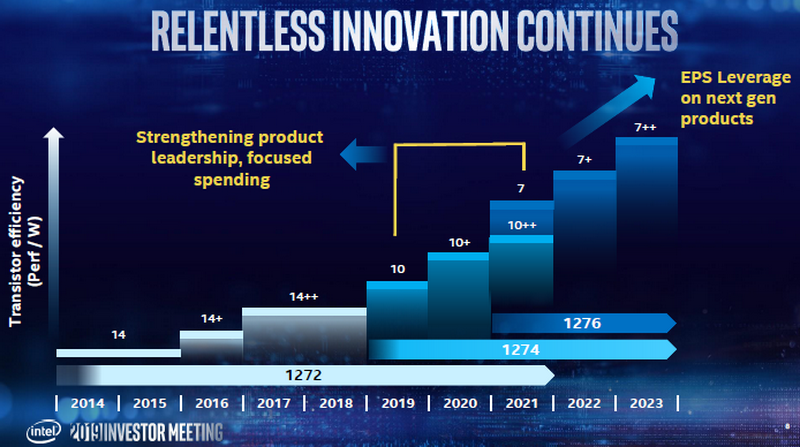

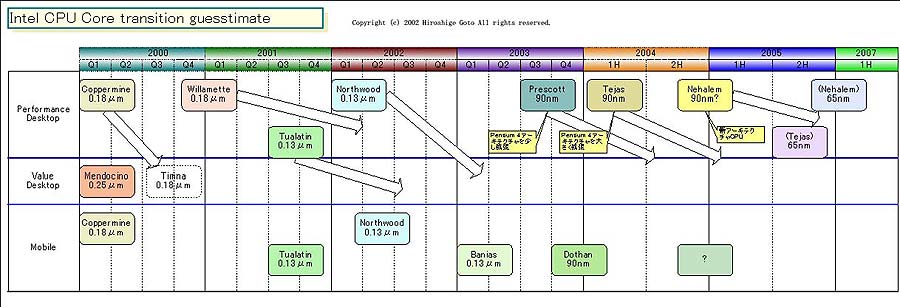

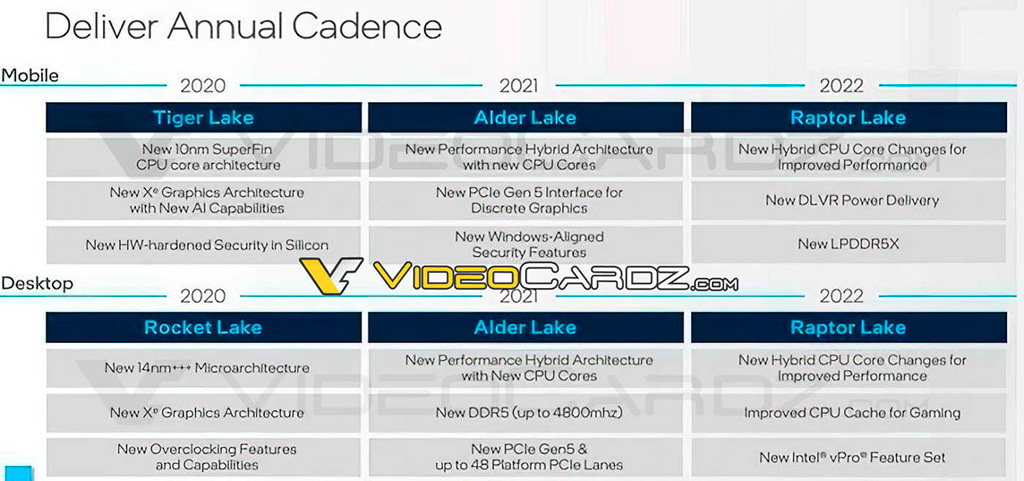

If you only take one thing away from this article, I’m going to put it here front and center. Here is what we’re seeing for Intel’s roadmaps, based on their disclosures today.

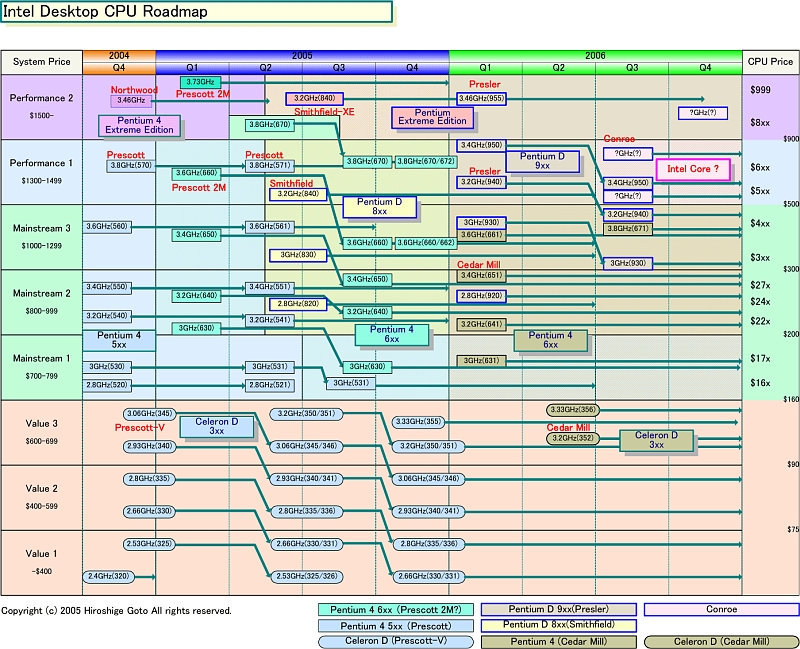

As always, there is a difference between when a technology ramps for production and comes to retail; Intel spoke about some technologies as ‘being ready’, while others were ‘ramping’, so this timeline is simply those dates as mentioned. As you might imagine, each process node is likely to exist for several years, this graph is simply showcasing the leading technology from Intel at any given time.

If you want the details on this graph, then read on.

Earlier this year, CEO Pat Gelsinger announced Intel’s new IDM 2.0 strategy, consisting of three elements:

- Build (7nm)

- Expand (TSMC)

- Productize (Intel Foundry Services)

The goal here is to continue to work on Intel’s process node technology development, going beyond the current 10nm designs in production today, but simultaneously using other foundry services from partners (or competitors) to regain/retain Intel’s position in its processors that drive a lot of the company revenue. The third element is IFS, Intel’s Foundry Services, where Intel is committing in a big way to opening up its manufacturing facilities to external semiconductor business.

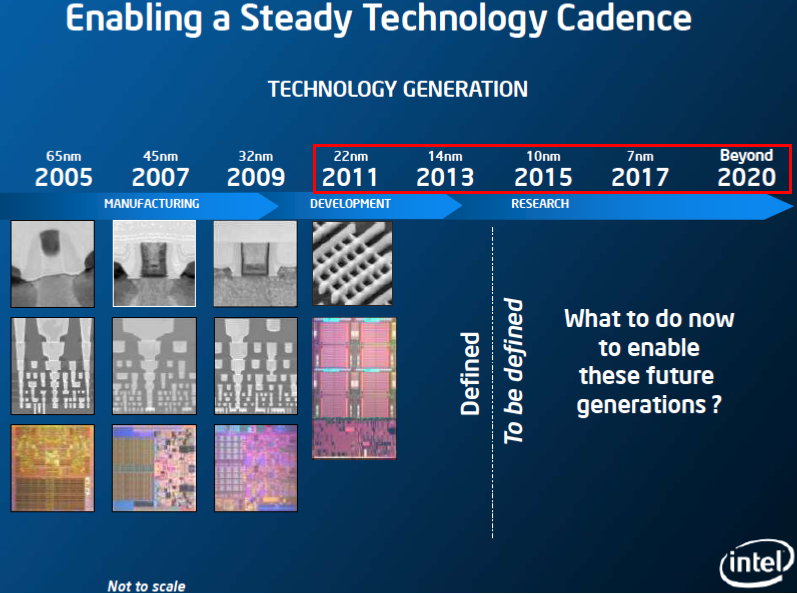

Underpinning (1) and (3) is how Intel executes on its own process node development. While in Intel’s recent Q3 2021 earnings call CEO Gelsinger confirmed that Intel is now producing more 10nm wafers in a day than 14nm wafers, marking a shift in confidence between the two designs, it is no secret that Intel has had difficulty in transitioning from its 14nm process to its 10nm process. On June 29th this year, Intel also stated that its next generation 10nm product requires additional validation time to streamline deployment on enterprise systems for 2022. Note that at the same time, TSMC has surpassed Intel by shipping at capacity with its equivalent designs (called 7nm) and its leading edge (5nm) designs that surpass Intel’s performance.

While in Intel’s recent Q3 2021 earnings call CEO Gelsinger confirmed that Intel is now producing more 10nm wafers in a day than 14nm wafers, marking a shift in confidence between the two designs, it is no secret that Intel has had difficulty in transitioning from its 14nm process to its 10nm process. On June 29th this year, Intel also stated that its next generation 10nm product requires additional validation time to streamline deployment on enterprise systems for 2022. Note that at the same time, TSMC has surpassed Intel by shipping at capacity with its equivalent designs (called 7nm) and its leading edge (5nm) designs that surpass Intel’s performance.

As with the previous announcement in March, Intel is reaffirming that it intends to return to leadership performance in semiconductors in 2025. This will enable both the company to compete better as it builds its own products (1) but also offer a wider portfolio of performance and technologies for its future IFS customers (3). To do this, it is realigning the roadmap for its future process node technologies to be more aggressive with improvements, yet at the same time more modular with its technology to enable faster transitions.

To do this, it is realigning the roadmap for its future process node technologies to be more aggressive with improvements, yet at the same time more modular with its technology to enable faster transitions.

Leading up this plan is Dr. Ann B Kelleher, who was named SVP and GM of the Technology Development division at Intel last year. This division is where all the research and development of Intel’s future process node technologies and enhancements comes from – it used to be part of Intel’s System Architecture Group, however it was split in July 2020 to re-establish a focus purely on Technology Development. Dr. Kelleher’s background involves process research in academia, followed by 26 years at Intel as a process engineer, moving up to managing Fab 24 in Ireland, Fab 12 in Arizona, Fab 11X in Rio Rancho, before landing in HQ in Oregon as the GM of Manufacturing and Operations.

Her experience covering both fab-scale production and process node research is going to be critical for Intel’s future plans. In discussing with Kelleher ahead of today’s announcements, she stated that she has implemented fundamental changes when it comes to supplier approach, ecosystem learnings, organizational changes, modular design strategies, contingency plans, and realigning the Technology Development Team into a more streamlined outfit ready to execute. These include key personnel such as Sanjay Natarajan as SVP and GM of Logic Development (one of Intel’s recent rehires) and Babak Sabi as CVP and GM of Assembly/Test Development

In discussing with Kelleher ahead of today’s announcements, she stated that she has implemented fundamental changes when it comes to supplier approach, ecosystem learnings, organizational changes, modular design strategies, contingency plans, and realigning the Technology Development Team into a more streamlined outfit ready to execute. These include key personnel such as Sanjay Natarajan as SVP and GM of Logic Development (one of Intel’s recent rehires) and Babak Sabi as CVP and GM of Assembly/Test Development

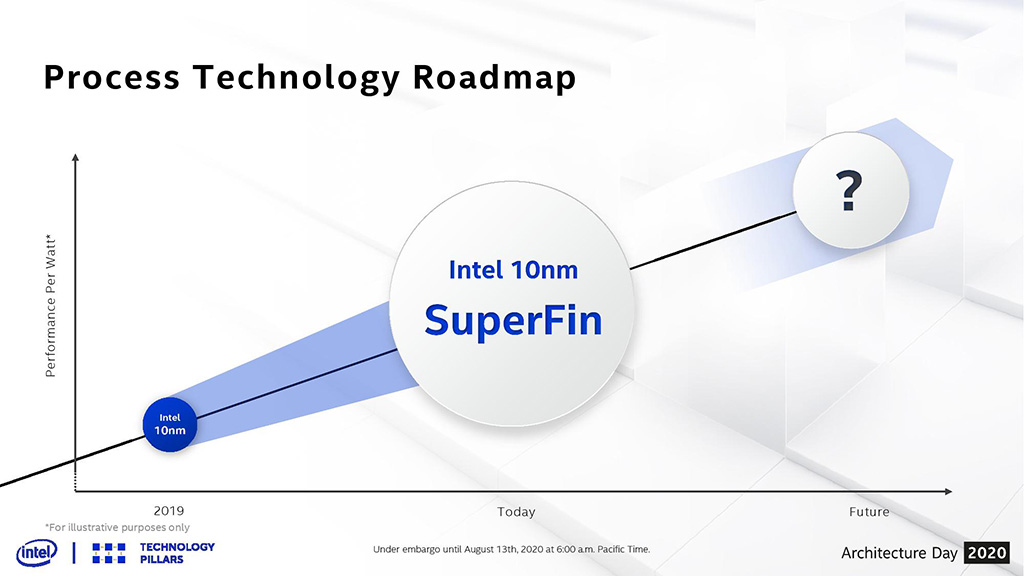

Intel is today defining ‘technology leadership by 2025’ as defined by the metric of performance per watt. We asked Intel is a pre-briefing what that means for peak performance, which is often a metric we care about for end product design, and the answer was that «peak performance remains a key part of Intel’s strategic development».

Intel Renames The Nodes: ‘Mine is Smaller’

The problem with simply posting Intel’s roadmap here is that the news is two-fold. Not only is Intel disclosing the state of its technology for the next several years, but the names of the technology are changing to better align with common industry norms.

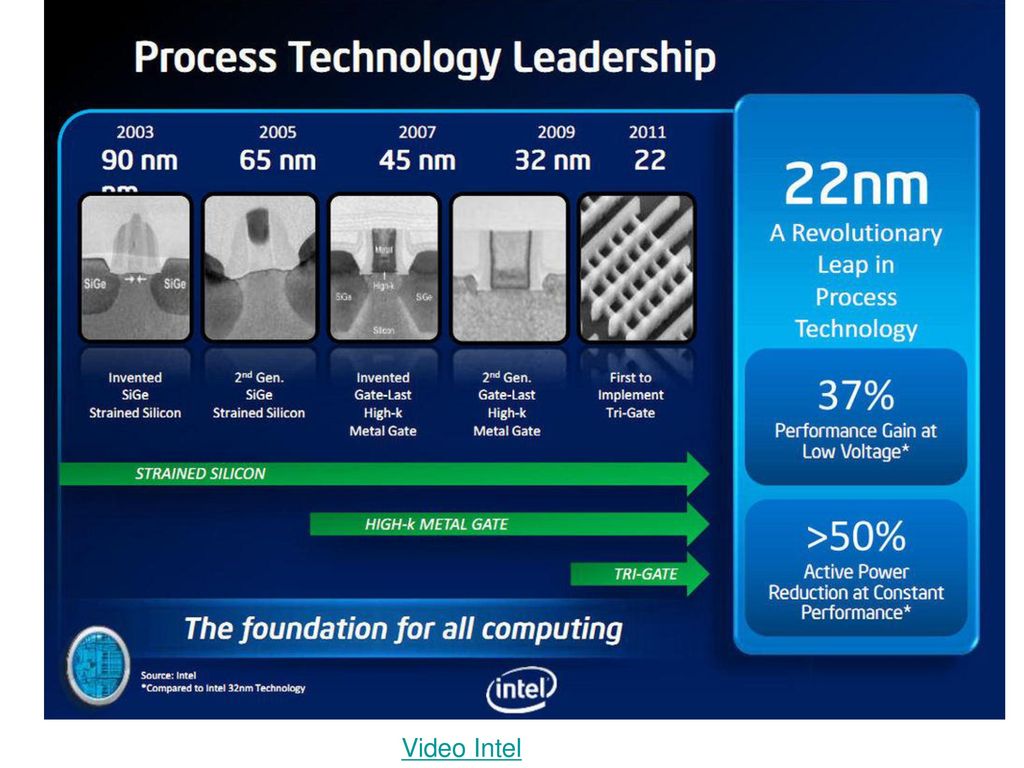

It is no secret that having «Intel 10nm» being equivalent to «TSMC 7nm», even though the numbers actually have nothing to do with the physical implementation, has ground at Intel for a while. A lot of the industry, for whatever reason, hasn’t learned that these numbers aren’t actually a physical measurement. They used to be, but when we moved from 2D planar transistors to 3D FinFET transistors, the numbers became nothing more than a marketing tool. Despite this, every time there’s an article about the technology, people get confused. We’ve been talking about it for half a decade, but the confusion still remains.

To that end, Intel is renaming its future process nodes. Here’s the roadmap image, but I’ll be breaking it down piece by piece.

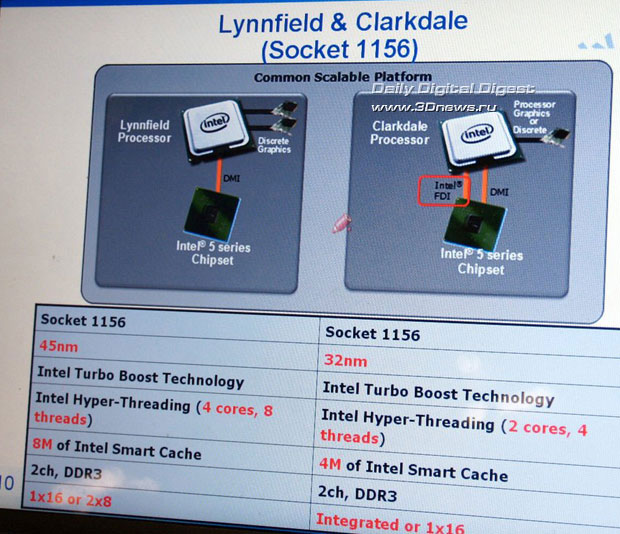

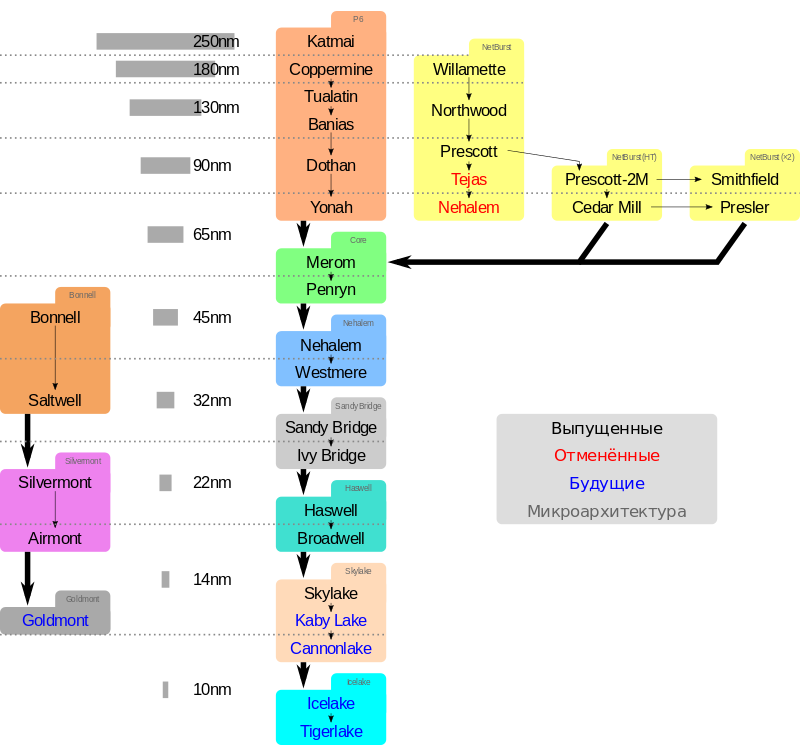

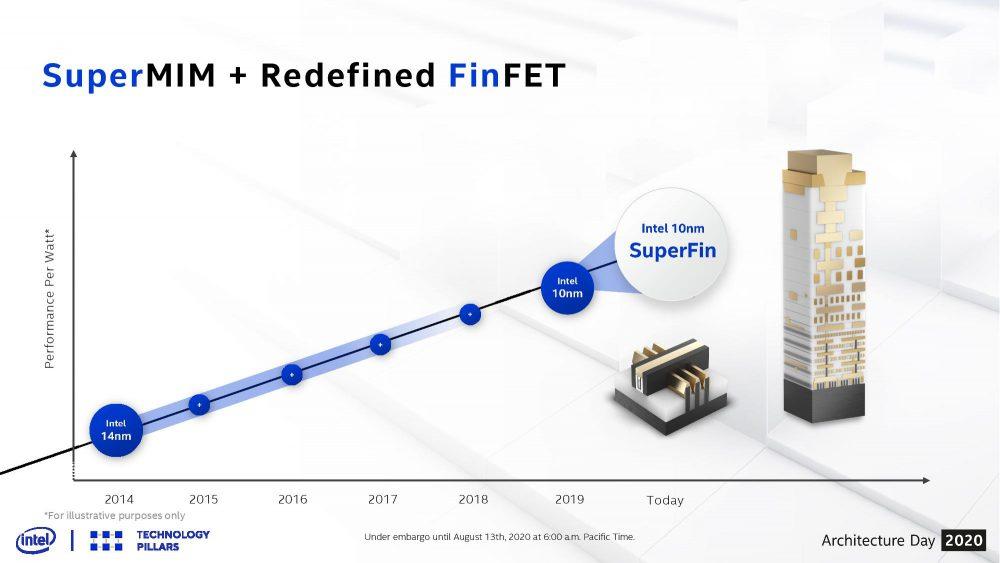

2020, Intel 10nm SuperFin (10SF): Current generation technology in use with Tiger Lake and Intel’s Xe-LP discrete graphics solutions (SG1, DG1). The name stays the same.

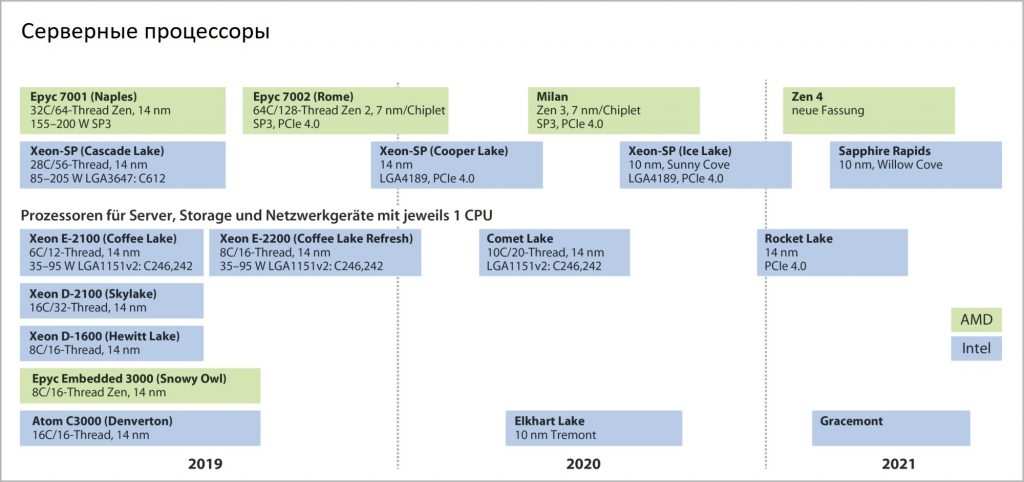

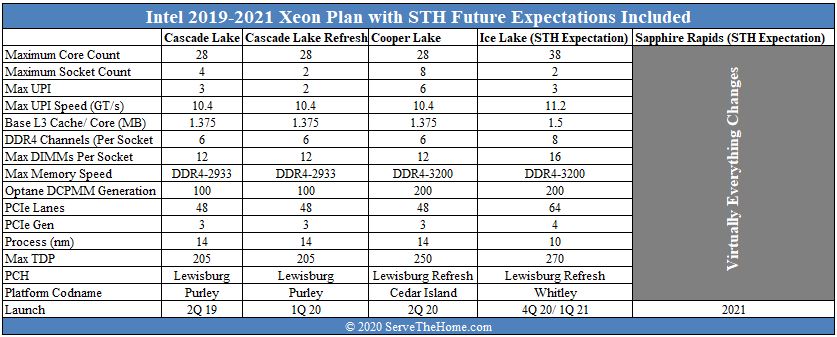

2021 h3, Intel 7: Previously known as 10nm Enhanced Super Fin or 10ESF. Alder Lake and Sapphire Rapids will now be known as Intel 7nm products, showcasing a 10-15% performance per watt gain over 10SF due to transistor optimizations. Alder Lake is currently in volume production. Intel’s Xe-HP will now be known as an Intel 7 product.

Alder Lake and Sapphire Rapids will now be known as Intel 7nm products, showcasing a 10-15% performance per watt gain over 10SF due to transistor optimizations. Alder Lake is currently in volume production. Intel’s Xe-HP will now be known as an Intel 7 product.

2022 h3, Intel 4: Previously known as Intel 7nm. Intel earlier this year stated that its Meteor Lake processor will use a compute tile based on this process node technology, and the silicon is now back in the lab being tested. Intel expects a 20% performance per watt gain over the previous generation, and the technology uses more EUV, mostly in the BEOL. Intel’s next Xeon Scalable product, Granite Rapids, will also use a compute tile based on Intel 4.

2023 h3, Intel 3: Previously known as Intel 7+. Increased use of EUV and new high density libraries. This is where Intel’s strategy becomes more modular – Intel 3 will share some features of Intel 4, but enough will be new enough to describe this a new full node, in particular new high performance libraries. Nonetheless, a fast follow on is expected. Another step up in EUV use, Intel expects a manufacturing ramp in the second half of 2023 with an 18% performance per watt gain over Intel 4.

Nonetheless, a fast follow on is expected. Another step up in EUV use, Intel expects a manufacturing ramp in the second half of 2023 with an 18% performance per watt gain over Intel 4.

2024, Intel 20A: Previously known as Intel 5nm. Moving to double digit naming, with the A standing for Ångström, or 10A is equal to 1nm. Few details, but this is where Intel will move from FinFETs to its version of Gate-All-Around (GAA) transistors called RibbonFETs. Also Intel will debut a new PowerVia technology, described below.

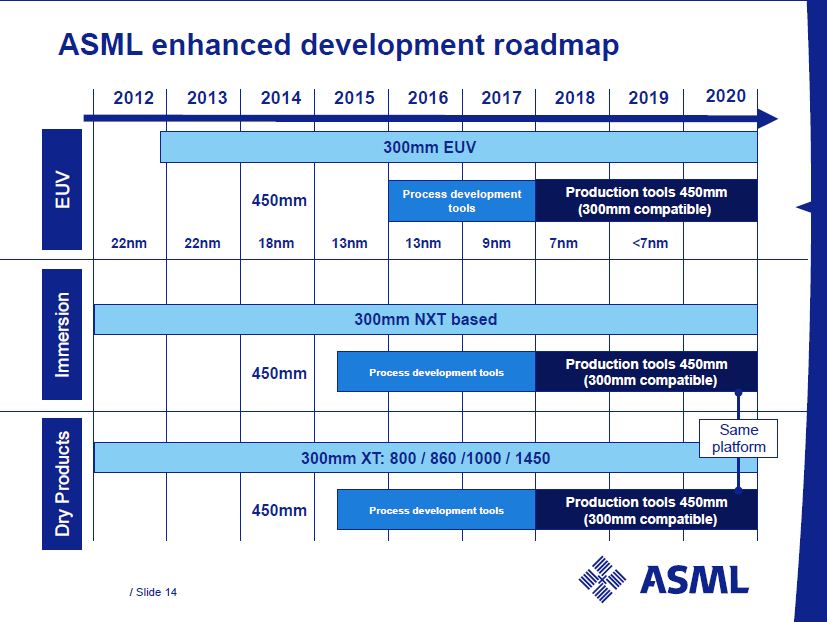

2025, Intel 18A: Not listed on the diagram above, but Intel is expecting to have an 18A process in 2025. 18A will be using ASML’s latest EUV machines, known as High-NA machines, which are capable of more accurate photolithography. Intel has stated to us that it is ASML’s lead partner when it comes to High-NA, and is set to receive the first production model of a High-NA machine. ASML recently announced High-NA was being delayed- when asked if this was an issue, Intel said no, as the timelines for High-NA and 18A are where Intel expects to intersect and have unquestioned leadership.

Intel has confirmed to us that Intel 3 and Intel 20A will be offered to foundry customers (but hasn’t stated if Intel 4 or Intel 7 will be).

To bring this altogether in a single table, with known products, we have the following:

| Intel’s Process Node Technology | ||||

| Old Name | New Name | Roadmap | Products | Features |

| 10SF | 10SF | Today | Tiger Lake SG1 DG1 Xe-HPC Base Tile Agilex-F/I FPGA |

SuperMIM Thin Film Barrier Volume 10nm On sale today |

| 10ESF | Intel 7 | 2021 h3 products | Alder Lake (21) Raptor Lake (22)? Sapphire Rapids (22) Xe-HP Xe-HPC IO Tile |

10-15% PPW Upgraded FinFET ADL in Ramp today |

| 7nm | Intel 4 | 2022 h3 ramp 2023 h2 products |

Meteor Compute Tile Granite Compute Tile |

20% PPW vs 7 More EUV Silicon in Lab |

| 7+ | Intel 3 | 2023 h3 products | — | 18% PPW vs 4 Area Savings More EUV New Perf Libraries Faster Follow On |

| 5nm | Intel 20A | 2024 | — | RibbonFET PowerVia |

| 5+ | Intel 18A | 2025 | Unquestioned Leadership | 2nd Gen Ribbon High NA EUV |

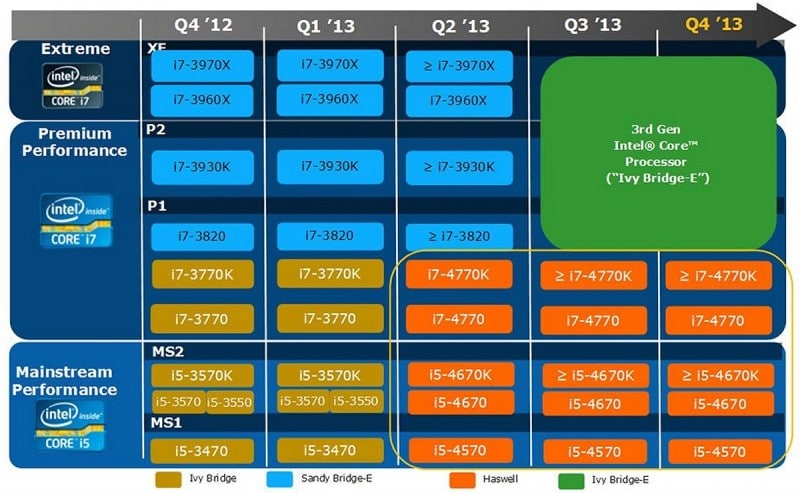

One of the issues here is the difference between a process node being ready, ramping production for product launches, and actually being made available. For example, Alder Lake (now on Intel 7nm) is due to come out this year, but Sapphire Rapids is going to be more of a 2022 product. Similarly, there are reports of Raptor Lake on Intel 7 coming out in 2022 to replace Alder Lake with the tiled Meteor Lake on Intel 4 in 2023. While Intel is happy to discuss process node development time frames, product timeframes are not as open (as no doubt customers would get frustrated if the time stated is missed).

For example, Alder Lake (now on Intel 7nm) is due to come out this year, but Sapphire Rapids is going to be more of a 2022 product. Similarly, there are reports of Raptor Lake on Intel 7 coming out in 2022 to replace Alder Lake with the tiled Meteor Lake on Intel 4 in 2023. While Intel is happy to discuss process node development time frames, product timeframes are not as open (as no doubt customers would get frustrated if the time stated is missed).

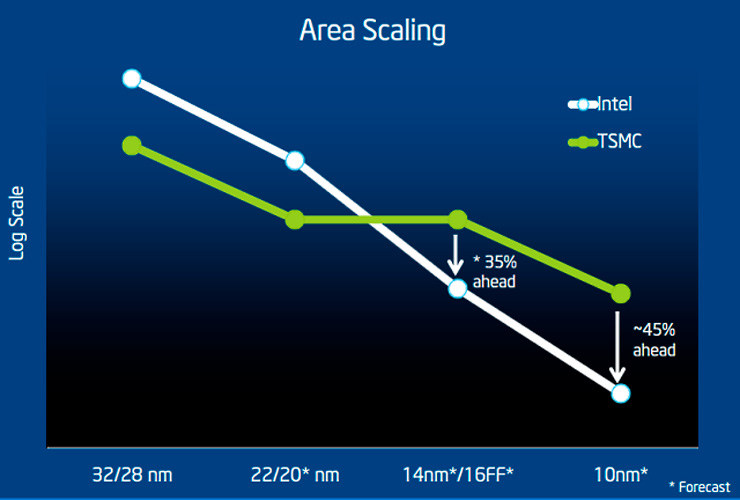

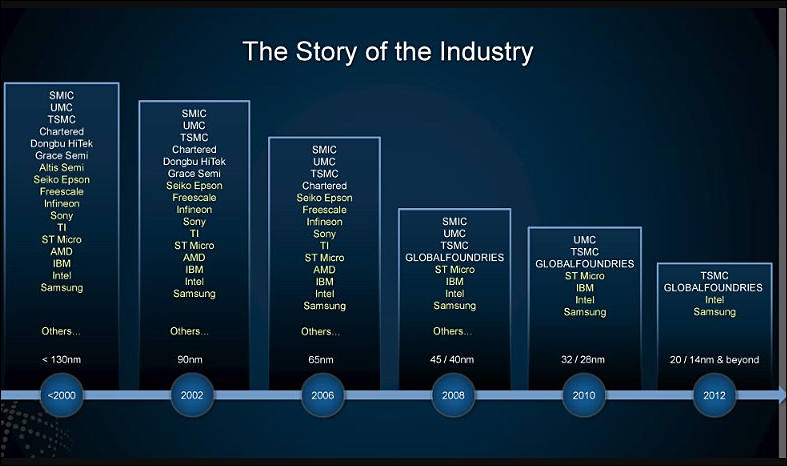

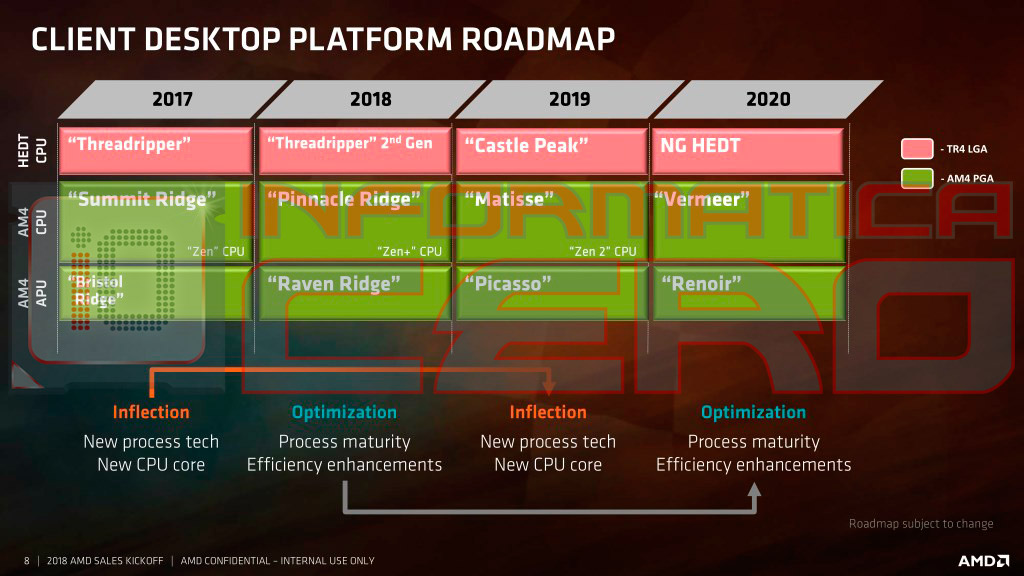

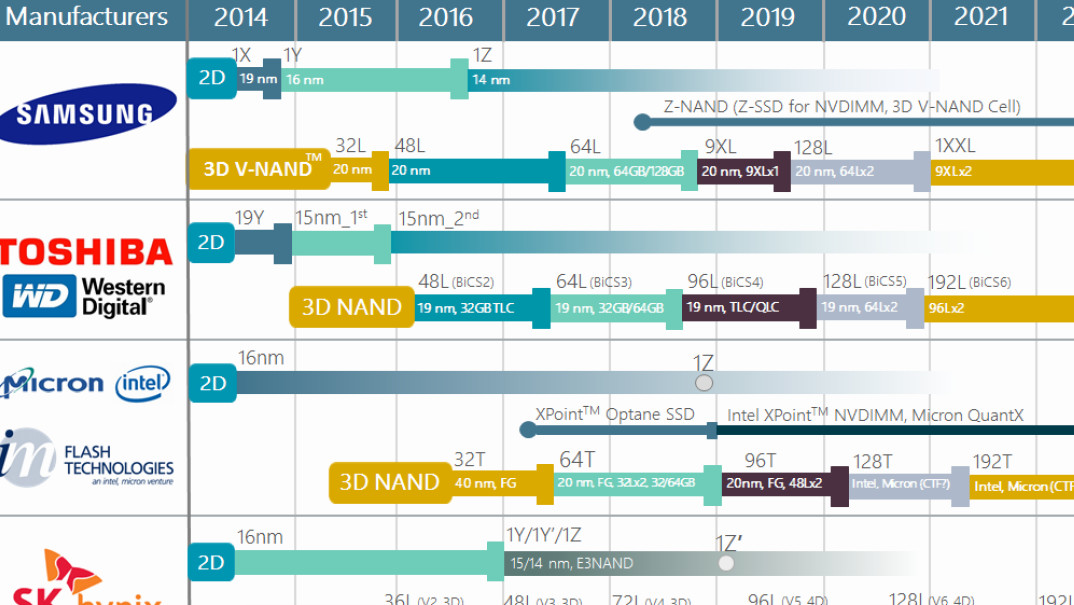

Why The Nodes Were Renamed

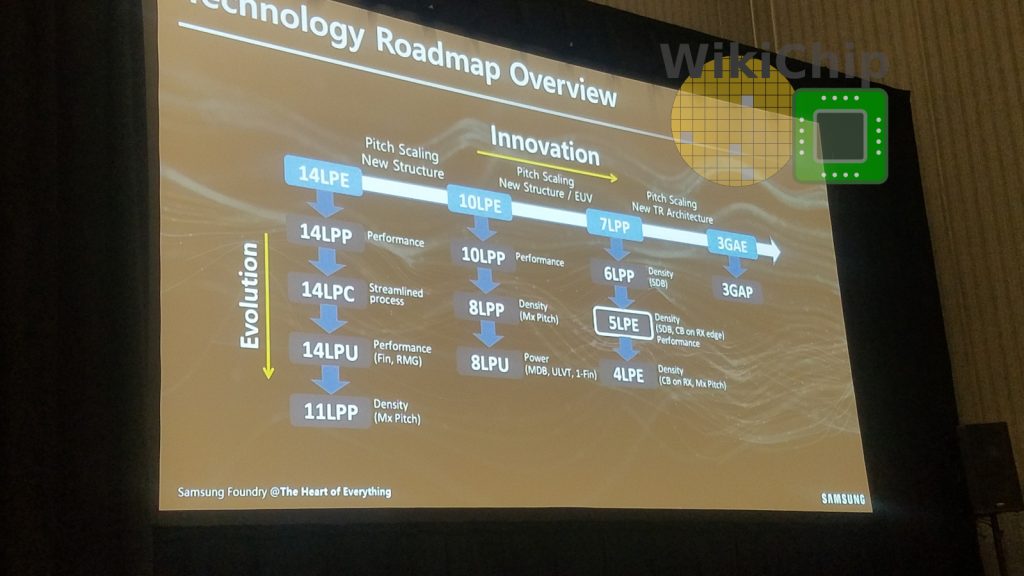

So as stated before, one element of renaming the nodes is due to matching parity with other foundry offerings. Both TSMC and Samsung, competitors to Intel, were using smaller numbers to compare similar density processes. With Intel now renaming itself, it gets more in-line with the industry. That being said, perhaps sneakily, Intel’s 4nm might be on par with TSMC’s 5nm, reversing the tables. By 3nm we expect there to be a good parity point, however that will depend on Intel matching TSMC’s release schedule.

Rather than throw process node names everywhere, it is typical to refer to peak quoted transistor densities instead. Here is the table we published in our recent IBM 2nm news post, but with an updated shift on Intel’s naming.

| 2021 Peak Quoted Transistor Densities (MTr/mm2) | ||||

| AnandTech Process Name |

IBM | TSMC | Intel | Samsung |

| 22nm | 16.50 | |||

| 16nm/14nm | 28.88 | 44.67 | 33.32 | |

| 10nm | 52.51 | 100.76 | 51.82 | |

| 7nm | 91.20 | 100.76 | 95.08 | |

| 5/4nm | 171.30 | ~200* | 126. 89 89 |

|

| 3nm | 292.21* | |||

| 2nm / 20A | 333.33 | |||

| Data from Wikichip, Different Fabs may have different counting methodologies * Estimated Logic Density |

||||

Exactly where Intel’s new 4nm and below will end up is yet to be disclosed, as numbers with stars alongside are based on estimates by the respective companies.

It has been expected for a while that Intel would be realigning its process node naming. Behind closed doors, I personally have been lobbying for it for a while, and I know that a few other journalists and analysts have been suggesting it to Intel as well. Some responses we received were related to apathy – one executive told me that «our customers that care about this actually know the difference», which is true for sure, but what we’re talking about here is more about perception in the wider ecosystem for enthusiasts and financial analysts who might not be up to speed. It is more or less a branding exercise, and I also told Intel that they are going to have to expect a mixed response – some voices might interpret the move as Intel trying to pull one over on the market, for example. But they’re going to have to live with it, as these are the new names.

It is more or less a branding exercise, and I also told Intel that they are going to have to expect a mixed response – some voices might interpret the move as Intel trying to pull one over on the market, for example. But they’re going to have to live with it, as these are the new names.

Meanwhile, despite Intel’s struggles with 10nm, it is still a process node in production and in volume production, in use for both consumer and enterprise devices, and it’s coming to desktops very soon. Even though it has some stiff competition from other players, it is still an offering in the market, and for those that want to compare process node densities using these names, it should have a moniker to avoid confusion. I am applauding that Intel is doing it sooner rather than later.

One key point to note is that the new Intel 7 node, which was formerly the 10ESF node, is not necessarily a «full» node update as we typically understand it. This node is derived as an update from 10SF, and as the diagram above states, will have ‘transistor optimizations’. Moving from 10nm to 10SF, that meant SuperMIM and new thin-film designs giving an extra 1 GHz+, however the exact details from 10SF to the new Intel 7 is unclear at this point. Intel has however stated that moving from Intel 7 to Intel 4 will be a regular full node jump, with Intel 3 using modular parts of Intel 4 with new high-performance libraries and silicon improvements for another jump in performance.

Moving from 10nm to 10SF, that meant SuperMIM and new thin-film designs giving an extra 1 GHz+, however the exact details from 10SF to the new Intel 7 is unclear at this point. Intel has however stated that moving from Intel 7 to Intel 4 will be a regular full node jump, with Intel 3 using modular parts of Intel 4 with new high-performance libraries and silicon improvements for another jump in performance.

We asked Intel if these process nodes will have additional optimization points, and were told that they will – whether any of them will be explicitly productized will depend on the features. Individual optimizations may account for an additional 5-10% performance per watt, and we were told that even 10SF (which keeps its name) has had several additional optimization points that haven’t necessarily been publicized. So whether these updates get marketed as 7+ or 7SF or 4HP is not known, but as with any manufacturing process as updates occur to help improve performance/power/yield, they get applied assuming the design adheres to the same rules.

«Isn’t Intel Just Trying To Pull The Wool Over Our Eyes?»

No.

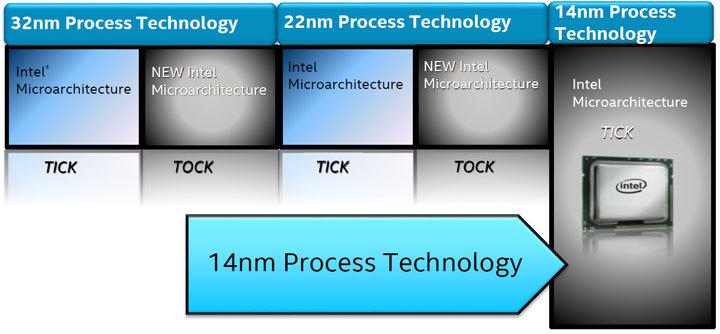

The problem here is that there is no consistent node naming between foundries. Intel has been saving any number change for major advances in its node manufacturing technology, instead using +/++ to signify improvements. If we compare this to TSMC and Samsung, both of whom have been happy to give half-node jumps new numbers entirely.

For example, Samsung’s 7LPP is a major node, however 6LPP, 5LPE and 4LPE are all iterative efforts on the same design (arguably also iterative of 8LPP), with 3GAE being the next major jump. Compare this to Intel, who was planning 10nm to 7nm to 5nm as major process node jumps – so while Samsung had one jump planned and 4 sub-variants (or more), Intel had two major jumps. Similarly, TSMC’s 10nm was a half-node jump over 16nm, while 16nm to 7nm was the full node – Intel made 14 to 10 to 7 as full nodes.

Intel stuck to its guns a long while, and delays to 10nm effectively hurt it in a multiplicative fashion. For example, if Intel had labeled 14+ as 13nm, and 14++ as 12nm, perhaps it wouldn’t be so bad. I mean, yes Intel should expect some hurt for 10nm being late, but when other foundries were showcasing smaller steps as full number jumps, it became a marketing and media nightmare. 14++++ became an industry joke, and coupled with how every time when they talked about future process nodes they had to cite the equivalent TSMC of Samsung process, it got a bit too much. It had to be explained every time, as new people come into the industry.

For example, if Intel had labeled 14+ as 13nm, and 14++ as 12nm, perhaps it wouldn’t be so bad. I mean, yes Intel should expect some hurt for 10nm being late, but when other foundries were showcasing smaller steps as full number jumps, it became a marketing and media nightmare. 14++++ became an industry joke, and coupled with how every time when they talked about future process nodes they had to cite the equivalent TSMC of Samsung process, it got a bit too much. It had to be explained every time, as new people come into the industry.

I’ve lobbied Intel to adjust its naming for a while, and I know other peers have as well. When we refer to Intel 7 from now on, we can draw equivalents to TSMC 7nm (even if TSMC is shipping 5nm in volume) without having to extensively explain differences in a simple name. This isn’t Intel pulling the wool over your eyes, or trying to hide a bad situation. This is Intel catching up to the rest of the industry in how these processes are named. To add to this, it’s a good thing that Intel is only renaming future nodes that haven’t reached the market yet.

This is a multi-page article!

Click the dropdown below for more pages, including

- This Page, New Node Names

- A Sidebar on Intel EUV and becoming ASML Lead Partner

- New for 2024: RibbonFETs and PowerVias

- Next Gen EMIB and Foveros Packaging

- Customers Customers Customers

Sidebar on Intel EUV and ASML

Intel’s Process Roadmap to 2025, with New Node NamesSidebar on Intel EUV and ASMLNew Technology Features for 2024: RibbonFETs and PowerViasIntel’s Next Generation Packaging: EMIB and FoverosCustomers

Tweet

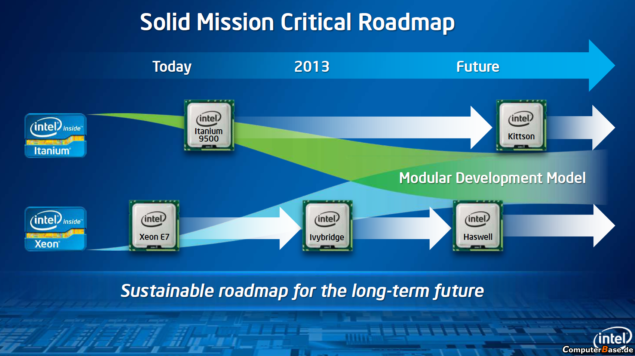

Intel Unveils 2021-2029 Process Roadmap

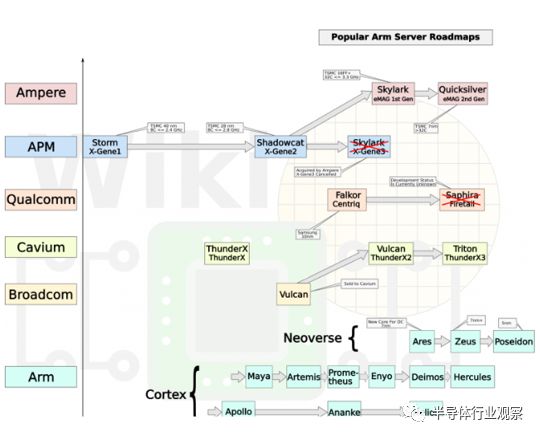

Back in May, Intel unveiled their process roadmap, highlighting their target plans up till 2023, but an even more detailed manufacturing roadmap has been revealed by Anandtech which shows a process roadmap path all the way up to 2029.

Intel Manufacturing Roadmap For The Next 10 Years Unveiled — 7nm in 2021, 5nm in 2023, 3nm in 2025, 2nm in 2027 and 1.

4 nm in 2029, Brand New Features and Back Porting

4 nm in 2029, Brand New Features and Back Porting

The roadmap is stated to have been unveiled at the IEEE International Electron Devices Meeting by one of Intel’s partners who stated that the said slide was first showcased by Intel themselves back in September. Intel already gave us a deep dive of their 7nm process plans but this slide goes even further than that. It’s a 10-year roadmap for what’s to come so let’s see what Intel has to offer us in the coming years.

Intel’s Process and Manufacturing Roadmap for the next 10 years shows 10nm, 7nm, 5nm, 3nm, 2nm, and 1.4nm. (Image Credits: Anandtech)

10nm to 1.4nm in The Next 10 Years

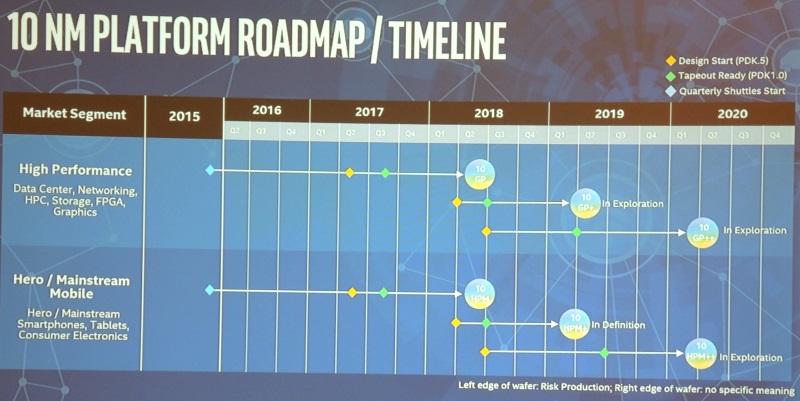

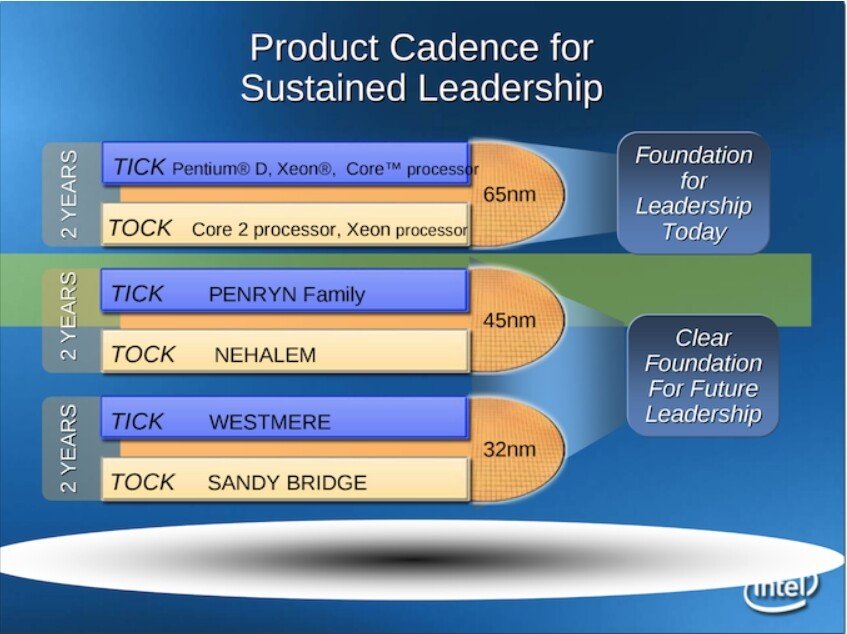

Starting off with the process roadmap, Intel will be following a 2-year cadence for each major node update. We got a soft launch of 10nm (10nm+) in 2019 which will be followed by 7nm in 2021, 5nm in 2023, 3nm in 2025, 2nm in 2027 and 1.4nm in 2029. What’s interesting here is that this 2-year cadence is referred to as the optimal cost-performance path by Intel themselves. So it would be Intel’s priority to follow this path, but there’s also a yearly cadence for the + / ++ nodes that offer more performance leverage and scalability opportunities on an existing node.

So it would be Intel’s priority to follow this path, but there’s also a yearly cadence for the + / ++ nodes that offer more performance leverage and scalability opportunities on an existing node.

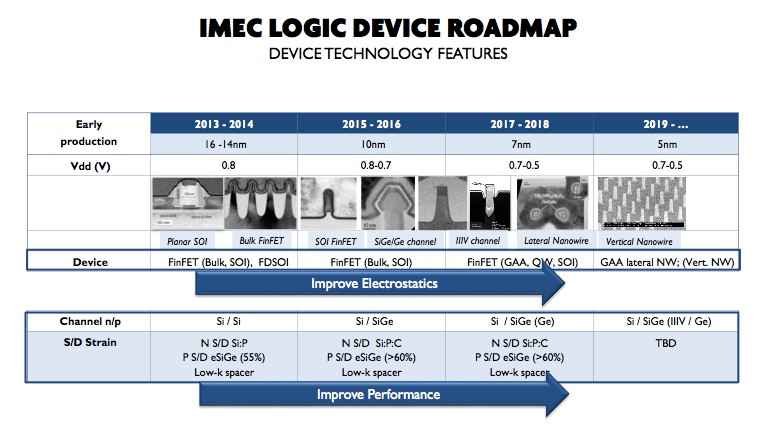

Before we talk about the optimized nodes for each process, we should focus on the key features that each major node update has to offer. For 7nm, Intel is saying the biggest feature is that it is made using EUV (Extreme ultraviolet lithography) technology. Similarly, all other major nodes will come with new features, but Intel hasn’t explicitly stated what new features we could expect. At the same time as Intel introduces their 10nm++ products, they will also have production and launch planned for their next-gen 7nm process node. The 10nm and 7nm nodes were already detailed by Intel during their 2019 Investors Meeting.

2 of 9

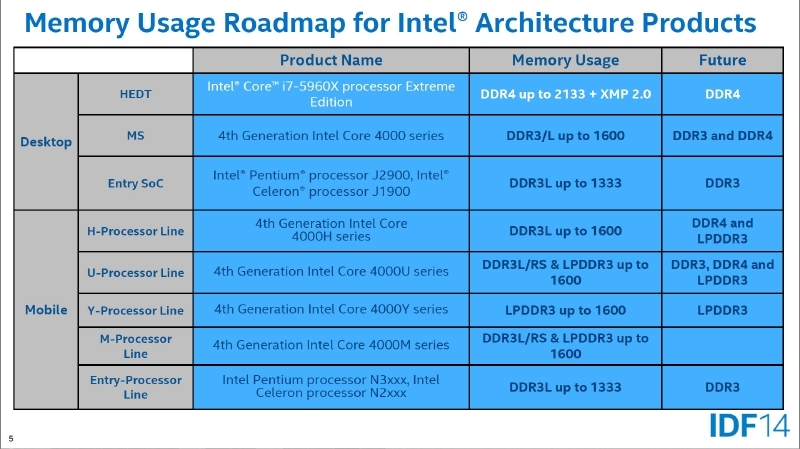

Intel 10nm, 10nm+ and 10nm++

Starting off with the 10nm family, Intel has clarified that their 10nm process node can deliver some major enhancements to performance per watt. Compared to 14nm++, the first iteration of 10nm is shown to be a good leap in efficiency and Intel plans to provide enhanced variants of 10nm moving forward with 10nm+ in 2019, 10nm++ in 2020, and 10nm+++ in 2021. Some of the major upgrades that 10nm would deliver include:

Compared to 14nm++, the first iteration of 10nm is shown to be a good leap in efficiency and Intel plans to provide enhanced variants of 10nm moving forward with 10nm+ in 2019, 10nm++ in 2020, and 10nm+++ in 2021. Some of the major upgrades that 10nm would deliver include:

- 2.7x density scaling vs 14nm

- Self-aligned Quad-Patterning

- Contact Over Active Gate

- Cobalt Interconnect (M0, M1)

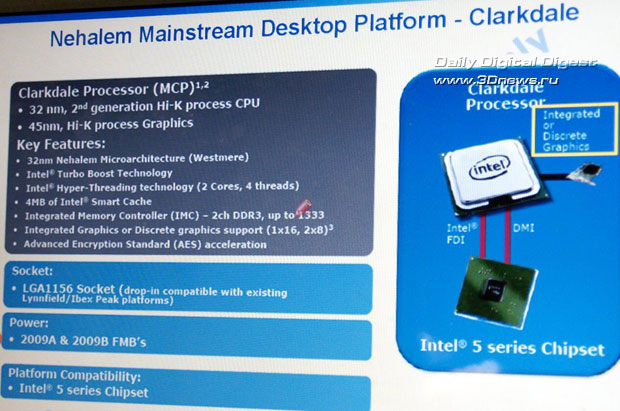

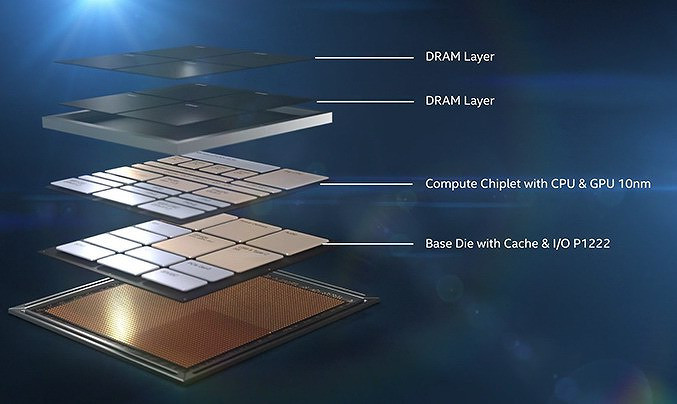

- 1st Gen Foveros 3D Stacking

- 2nd Gen EMIB

Intel 7nm, 7nm+ and 7nm++

At the same time as Intel introduces their 10nm+++ products, they will also have production and launch planned for their next-gen 7nm process node. Intel would continue to offer optimizations of the 7nm process node with 7nm+ in 2022 and 7nm++ in 2023. Just like 10nm, 7nm will deliver a good list of enhancements over 10nm which will include:

- 2x density scaling vs 10nm

- Planned intra-node optimizations

- 4x reduction in design rules

- EUV

- Next-Gen Foveros & EMIB Packaging

Do note that 10nm is the only process with a +++ optimization since it is already on 10nm+ in 2019. 1.4nm in 2029 looks to be very promising but Intel has had previous roadmaps stating that said we would get 10nm by 2015 and nm by 2017. But, more recently, Intel’s CEO, Bob Swan, stated that his company is all set to tackle TSMC with their first 7nm products tackling TSMC’s 5nm by Q4 2021 and expects to hit 5nm which he states is equivalent to TSMC’s 3nm node by the second half of 2024 and product availability in 2025.

1.4nm in 2029 looks to be very promising but Intel has had previous roadmaps stating that said we would get 10nm by 2015 and nm by 2017. But, more recently, Intel’s CEO, Bob Swan, stated that his company is all set to tackle TSMC with their first 7nm products tackling TSMC’s 5nm by Q4 2021 and expects to hit 5nm which he states is equivalent to TSMC’s 3nm node by the second half of 2024 and product availability in 2025.

Back Porting To Each Tail-End Optimization Node

The slide also talks about back porting which has been one of the interesting topics to discuss in recent months considering all the ruckus surrounding 14nm and 10nm nodes. Each major node has been shown to include at least two optimizations. 10nm+ will get 10nm++ and 10nm+++, 7nm will get 7nm+ (2022) and 7nm++ (2023), 5nm will get 5nm+ (2024) and 5nm++ (2025), 3nm will get 3nm+ (2026) and 3nm++ (2027) while 2nm will also get 2nm+ (2028) and 2nm++ (2029). There’s no optimized path for 1.4nm mentioned but then again, this slide only covers a 10-year roadmap so you can in the least expect an optimized node path for 1. 4nm too.

4nm too.

So each major node will be followed by an optimized ‘+’ node in the coming year and a further tail-end optimized ‘++’ node after that. Here’s the interesting thing, the ‘++’ or in the case of 10nm, +++ node, will launch alongside the next major node. The optimized node will have some advantages over the new node such as frequency and scalability from the previous two updates along with a higher number of yields.

So here, Intel can decide to make some interesting choices as they have multiple paths to choose from on each node generation. Now, given the timeframe of this roadmap, Intel may already have decided what’s next for 10nm and 7nm.

A picture a wafer from Intel’s foundry that was fabricated on the 14nm process.

Intel also talks about back porting on an older yet optimized node. A 7nm product can be back ported to 10nm+++, a 5nm product can be back ported to 7nm++, a 3nm product can be back ported to 3nm++ and a 2nm product can be back ported to 3nm++. There’s no back porting mentioned for the 1. 4nm node.

4nm node.

There have been recent rumors and talks regarding Intel back porting a 10nm++ product (Tiger Lake) to 14nm+++ (Rocket Lake). Substantial evidence has been found, but since the product is aiming a 2021 launch, there’s no official word from Intel on the matter. But, given that this roadmap talks about back porting, we may indeed see Rocket Lake CPUs featuring a back port of the Willow Cove cores that are to utilize a 10nm++ node on the mobility platform.

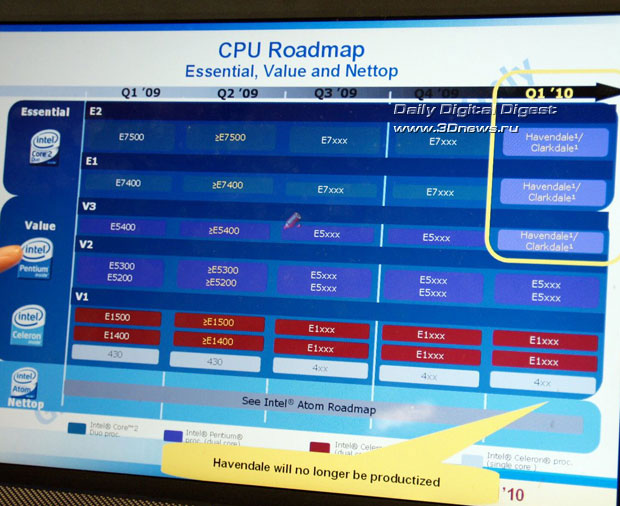

New Naming Scheme, 10nm ESF Now Intel 7, 7nm Now Intel 4, Intel 3, Intel 20A & Beyond

During its IDM 2.0 keynote, Intel’s CEO, Pat Gelsinger, unveiled his company’s brand new process roadmap along with a refreshing new naming scheme for next-generation nodes. The brand new roadmap covers all nodes and the respective products that we can expect to enter manufacturing and production through 2025 and beyond.

Intel Process Roadmap & Innovation Roadmap Highlights Brand New Node Naming Scheme, Drops ‘++’ & ‘SuperFin’ Brandings

Intel is restructuring as a whole under its new leadership and it looks like the process nodes, that have been confusing over the past few years, will finally be understandable for the general public. Intel recently has its 10nm SuperFin process node which is an enhanced variant of the Intel 10nm (++) node utilized by Ice Lake chips. Currently, Intel has both 10nm and 14nm chips within mobile and desktop platforms but that’s going to change later this year when Intel finally brings forth its Alder Lake and Sapphire Rapids lineup.

Intel recently has its 10nm SuperFin process node which is an enhanced variant of the Intel 10nm (++) node utilized by Ice Lake chips. Currently, Intel has both 10nm and 14nm chips within mobile and desktop platforms but that’s going to change later this year when Intel finally brings forth its Alder Lake and Sapphire Rapids lineup.

Under IDM 2.0, our factory network continues to deliver and we are now manufacturing more 10-nanometer wafers than 14-nanometer. As 10-nanometer volumes ramp, economics are improving with 10-nanometer wafer cost 45% lower year-over-year with more to come.

via Intel

Intel 7 Process Node (Previously 10nm Enhanced SuperFin)

So first up, we have Intel 7, a new name for the company’s 10nm Enhanced SuperFin process node. This node was going to power Intel’s Alder Lake Client and Sapphire Rapids Server lineup. Based on what Intel has stated, the node will offer a 10-15% performance per watt gain over 10nm SuperFin and feature FinFET transistor optimizations. Intel 7 is ready for volume production and the first products are expected to land on market by Q4 2021

Intel 7 is ready for volume production and the first products are expected to land on market by Q4 2021

Intel 7 delivers an approximately 10% to 15% performance-per-watt increase versus Intel 10nm SuperFin, based on FinFET transistor optimizations. Intel 7 will be featured in products such as Alder Lake for client in 2021 and Sapphire Rapids for the data center, which is expected to be in production in the first quarter of 2022.

2 of 9

Intel 4 Process Node (Previously 7nm)

Intel 4 is also something that the company has previously referred to as its 7nm process node. This is a much hyped-up node as it powers several next-generation products including Ponte Vecchio & along with that, we have Meteor Lake for Client and Granite Rapids for datacenters. Intel is claiming a 20% performance per watt gain for Intel 4 over Intel 7. In addition to these, Intel 4 will deliver a good list of enhancements over 10nm which will include:

- 2x density scaling vs Intel 7

- Planned intra-node optimizations

- 4x reduction in design rules

- EUV

- Next-Gen Foveros & EMIB Packaging

2 of 9

The node will also make full use of EUV Lithography and already has products taping out such as the Meteor Lake Compute Tile which was taped out during the previous quarter. Granite Rapids will also feature a multi-compute tile design and its main Granite Rapids core will be fabricated on the Intel 4 node.

Granite Rapids will also feature a multi-compute tile design and its main Granite Rapids core will be fabricated on the Intel 4 node.

Intel 4 fully embraces EUV lithography to print incredibly small features using ultra-short wavelength light. With an approximately 20% performance-per-watt increase, along with area improvements, Intel 4 will be ready for production in the second half of 2022 for products shipping in 2023, including Meteor Lake for client and Granite Rapids for the data center.

Intel 3 Process Node (An Intel 4 Optimization?)

Moving beyond Intel 4, the company plans to launch its Intel 3 process node which would be ready for manufacturing products by the second half of 2023. Based on everything that Intel has listed, it looks like Intel 3 is a generational optimization of Intel 4 as it delivers an 18% performance per watt gain, offers denser HP libraries, increases the intrinsic driver current, increased EUV use & reduces via resistance.

It looks like everything beyond Meteor Lake (Lunar Lake) and Granite Ridge (Diamond Rapids) could utilize the Intel 3 process node though we are talking about products that would launch in 2024 or even 2025 by the earliest so there’s a long way to go.

Intel 3 leverages further FinFET optimizations and increased EUV to deliver an approximately 18% performance-per-watt increase over Intel 4, along with additional area improvements. Intel 3 will be ready to begin manufacturing products in the second half of 2023.

Intel 20A Process Node & Beyond (A True Next-Gen Node)

Intel has gone ahead to talk about its post-nanometer era with a new product it is referring to as Intel 20A. The Intel 20A starts the Angstrom era (A for Angstrom) which is equal to 10⁻¹⁰ m or 1A = 0.1nm. This is just a cool way of saying 2nm but given how small nodes have gotten and the fact that we are heading down to decimal spaces within this decade, Intel decided a new measuring unit was needed.

2 of 9

So Intel 20A (2nm) is going to offer breakthrough innovations when it enters the early production phase by 1H 2024. The 20A node is expected to feature brand new RibbonFET transistors that will replace the existing FinFET architecture and also deliver new interconnect innovations, one of which is known as PowerVia. Intel is also expanding upon its Forveros technologies with Omni and Direct. Forveors Omni will be featured in products that package high-performance compute tiles while Forveors Direct will allow multi-tier interconnector resistance through a copper to copper bond. Forveros as a whole will be updated to deliver increased bandwidth through next-gen inter-connect solutions.

2 of 9

Intel 20A ushers in the angstrom era with two breakthrough technologies, RibbonFET and PowerVia. RibbonFET, Intel’s implementation of a gate-all-around transistor, will be the company’s first new transistor architecture since it pioneered FinFET in 2011.

The technology delivers faster transistor switching speeds while achieving the same drive current as multiple fins in a smaller footprint. PowerVia is Intel’s unique industry-first implementation of backside power delivery, optimizing signal transmission by eliminating the need for power routing on the front side of the wafer. Intel 20A is expected to ramp in 2024.

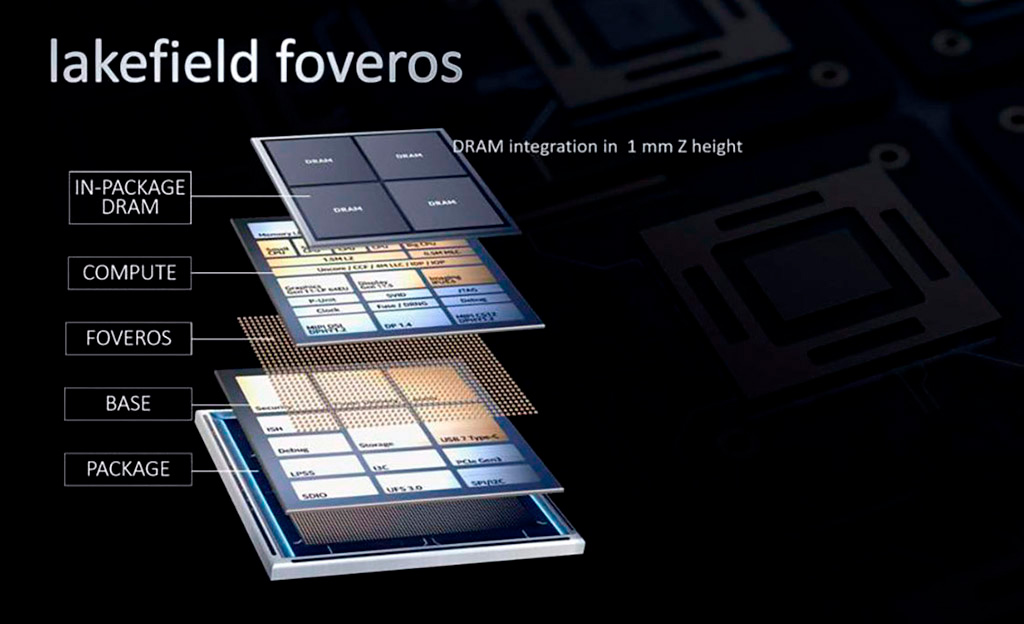

- Foveros Omni ushers in the next generation of Foveros technology by providing unbounded flexibility with performance 3D stacking technology for die-to-die interconnect and modular designs. Foveros Omni allows die disaggregation, mixing multiple top die tiles with multiple base tiles across mixed fab nodes and is expected to be ready for volume manufacturing in 2023.

- Foveros Direct moves to direct copper-to-copper bonding for low-resistance interconnects and blurs the boundary between where the wafer ends and where the package begins. Foveros Direct enables sub-10 micron bump pitches providing an order of magnitude increase in the interconnect density for 3D stacking, opening new concepts for functional die partitioning that were previously unachievable.

Foveros Direct is complementary to Foveros Omni and is also expected to be ready in 2023.

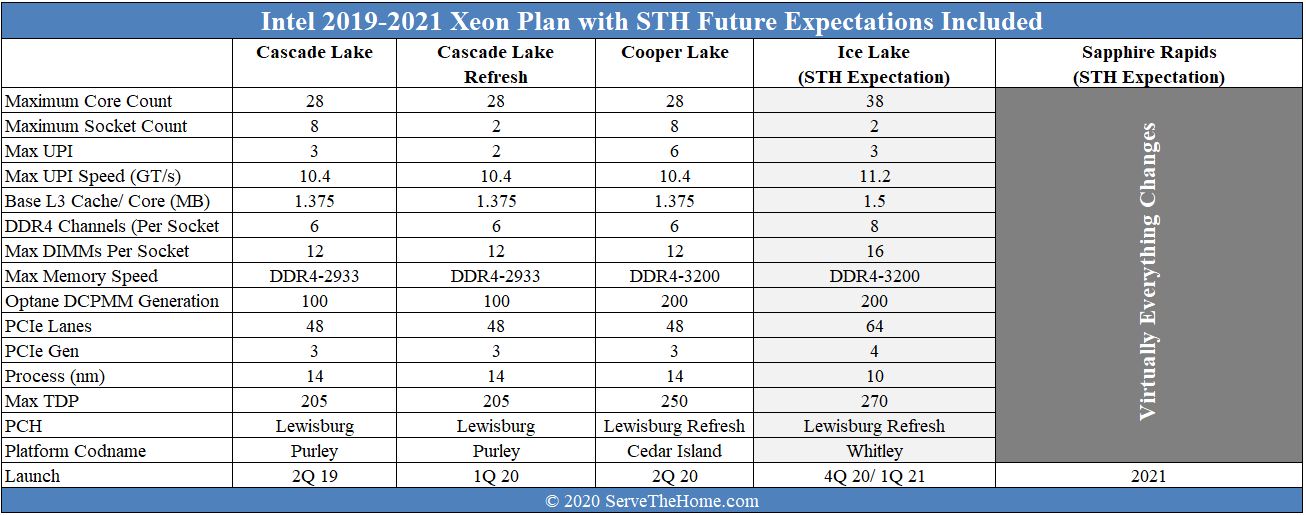

Intel Process Roadmap

| Process Name | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| Production | In High-Volume (Now) | In Volume (Now) | 2H 2022 | 2H 2023 | 2H 2024 | 2H 2025 |

| Perf/Watt (over 10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | TBA |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| Transistor Architecture | FinFET | Optimized FinFET | Optimized FinFET | Optimized FinFET | RibbonFET | Optimized RibbonFET |

| Products | Tiger Lake | Alder Lake Raptor Lake Sapphire Rapids Emerald Rapids Xe-HPG? |

Meteor Lake Xe-HPC / Xe-HP? |

Granite Rapids Sierra Forest TBA |

Arrow Lake Diamond Rapids? TBA |

Lunar Lake Nova Lake TBA TBA |

As for products based on the Intel 20A process node, don’t expect them to be a reality prior to 2025. Also, based upon the older roadmaps and where 20A is positioned, it looks to be either a rename of Intel’s 5nm or 3nm process node. but more scaled up to add in the ‘+’ optimizations which have been excluded from now onwards.

Also, based upon the older roadmaps and where 20A is positioned, it looks to be either a rename of Intel’s 5nm or 3nm process node. but more scaled up to add in the ‘+’ optimizations which have been excluded from now onwards.

Intel doesn’t stop at 20A though, they go on to discuss next-generation nodes through 2025 and beyond which would include 18A. The 18A node is already in development for early 2025 and will feature refinements to the RibbonFET architecture to deliver another major leap in transistor and chip performance.

Intel’s Process and Manufacturing Roadmap for the next 10 years shows 10nm, 7nm, 5nm, 3nm, 2nm, and 1.4nm. (Image Credits: Anandtech)

These new innovations and naming schemes are great to avoid the mess that Intel was headed into just a few years back. The company had process node roadmaps lineup with several nodes & their respective backports + optimizations in a really confusing manner. Now, Intel can move forward without worrying about the naming schemes and offer a unified process node lineup under its new naming criteria.

Intel’s foundry roadmap lays out the post-nanometer “Angstrom” era

It’s so tiny —

Ron Amadeo

—

-

Intel’s graph of the past and future.

Intel

-

RibbonFET (or a gate-all-around transistor) lets you stack up channels vertically, making for a smaller footprint.

Intel

-

Intel’s description: «The image at left shows a design with power and signal wires intermingled on the top of the wafer. The image at right shows the new PowerVia technology, Intel’s unique industry-first implementation of a backside power delivery network.

«

«Intel

Earlier this year, Intel got a new CEO and kicked off a new business plan that would open its foundries to other chip-design firms, the same way TSMC and Samsung Semiconductor operate. At its «Intel Accelerated» event today, the company laid out a roadmap for its future as a for-hire foundry. Besides the future of ever-smaller process nodes, the company also announced it has scored one of the world’s biggest chip designers, Qualcomm, as a future foundry customer.

As part of entering the foundry market, Intel will start naming its process nodes more like its rivals. The process-node numbers used for chips like «5nm» started out life as a measurement of transistor size, but eventually the marketers got hold of them and companies started cheating down their numbers to look more advanced. Intel says its new naming scheme will better align with how TSMC and Samsung talk about their foundry technologies. Gone are the days of «Intel 10nm Enhanced Super Fin»—instead, the node is called «Intel 7.» It should have a comparable density to the TSMC and Samsung 7 nm nodes and will be ready for production in Q1 2022 (TSMC and Samsung are currently shipping «5nm» products). «Intel 4″—which Intel previously called «7nm»—is now said to be equivalent to TSMC and Samsung’s 4 nm node, and it will begin manufacturing products in 2023.

Gone are the days of «Intel 10nm Enhanced Super Fin»—instead, the node is called «Intel 7.» It should have a comparable density to the TSMC and Samsung 7 nm nodes and will be ready for production in Q1 2022 (TSMC and Samsung are currently shipping «5nm» products). «Intel 4″—which Intel previously called «7nm»—is now said to be equivalent to TSMC and Samsung’s 4 nm node, and it will begin manufacturing products in 2023.

If you’re wondering what happens when we run out of «nm» numbers, Intel’s sales pitch for that is the «Angstrom» era, a unit of measurement that is one-tenth of a nanometer. In 2024, the company wants to ramp up the «Intel 20A» process node. (So, a «2nm» equivalent, but Intel was calling this node «5nm» previously. Also, remember, these are marketing numbers and not really units of measurement.) In early 2025 the company will be working on «Intel 18A.»

The name change to «Intel 20A» instead of «2nm» seems to partly be because that process node will include some major architectural changes for Intel’s chips. For years, the company has used FinFET transistors, but for Intel 20A the company will switch to a gate-all-around (GAA) design it’s calling «RibbonFET.» FinFETs would scale channel-current capacity by adding multiple fins and, therefore, more horizontal space. But GAA designs allow chip manufacturers to stack multiple channels on top of each other, making current capacity a vertical problem and increasing chip density. Intel 20A will also introduce «PowerVias,» a new chip-design method that will put power delivery on the backside of the chip. This design would put the power-delivery layer on the bottom of the chip, then the transistors, then the communication wires. Traditional chip design puts the transistors at the bottom, and higher-up signal and power layers have to intermingle to reach the transistor layer.

For years, the company has used FinFET transistors, but for Intel 20A the company will switch to a gate-all-around (GAA) design it’s calling «RibbonFET.» FinFETs would scale channel-current capacity by adding multiple fins and, therefore, more horizontal space. But GAA designs allow chip manufacturers to stack multiple channels on top of each other, making current capacity a vertical problem and increasing chip density. Intel 20A will also introduce «PowerVias,» a new chip-design method that will put power delivery on the backside of the chip. This design would put the power-delivery layer on the bottom of the chip, then the transistors, then the communication wires. Traditional chip design puts the transistors at the bottom, and higher-up signal and power layers have to intermingle to reach the transistor layer.

Advertisement

If Intel actually manages to stick to its roadmap, it should be able to count Qualcomm as an interested customer. President and CEO Cristiano Amon expressed interest in the «20A» node, saying, «Qualcomm is excited about the breakthrough RibbonFET and PowerVia technologies coming in Intel 20A. We’re also pleased to have another leading-edge foundry partner enabled by IFS [Intel Foundry Services] that will help the U.S. fabless industry to bring its products to an onshore manufacturing site.»

We’re also pleased to have another leading-edge foundry partner enabled by IFS [Intel Foundry Services] that will help the U.S. fabless industry to bring its products to an onshore manufacturing site.»

Today, Qualcomm makes a lot of chips and is a customer of both TSMC and Samsung. The two companies regularly compete for each new design in Qualcomm’s lineup, with industry reports often describing a down-to-the-wire horse race of one beating the other. Whether or not Intel will be in the mix for most of these foundry battles depends on if it can catch up to TSMC and Samsung. At least now, Qualcomm is offering Intel a spot in the race instead of smartphone irrelevance.

Listing image by Intel

Ron Amadeo

Ron is the Reviews Editor at Ars Technica, where he specializes in Android OS and Google products. He is always on the hunt for a new gadget and loves to rip things apart to see how they work.

Advertisement

← Previous story Next story →

Intel Process Roadmap Through 2025: Renamed Process Nodes, Angstrom Era Begins

Skip to main content

Tom’s Hardware is supported by its audience. When you purchase through links on our site, we may earn an affiliate commission. Here’s why you can trust us.

When you purchase through links on our site, we may earn an affiliate commission. Here’s why you can trust us.

(Image credit: Intel)

Intel CEO Pat Gelsinger whipped the covers off the company’s new process and packaging roadmap that now stretches out to 2025, outlining an annual cadence of the company’s future process nodes spanning from standard nanometer-scale tech down to incredibly small angstrom-class transistors. Intel also teased the first details of its angstrom-class (the next measurement below nanometer) technology, like RibbonFET, its first new transistor design since FinFET arrived a decade ago, and PowerVia, a new backside power delivery technique that sandwiches the transistors between layers of wiring. Intel will also change its process node naming scheme again, this time to match the naming used by external foundries like TSMC. That re-branding begins with Intel’s 10nm Enhanced SuperFin, which will now be renamed to ‘Intel 7.’

Intel says its process tech will match the current industry leader, TSMC, by 2024, and that it will retake ‘process performance leadership’ by 2025, helped along by being the first company to receive a next-gen High NA EUV machine from ASML for its next-gen chips. Intel also shared details of its future Foveros Omni and Direct technologies during its ‘Intel Accelerated’ webcast and announced that its Sapphire Rapids chips would be the «first dual-reticle-sized device» in the industry.

Intel also shared details of its future Foveros Omni and Direct technologies during its ‘Intel Accelerated’ webcast and announced that its Sapphire Rapids chips would be the «first dual-reticle-sized device» in the industry.

Intel’s fledging foundry services business also notched two big wins, with AWS announcing that it will use Intel’s packaging services while Qualcomm announced that it will explore using Intel’s 20A process for future chip designs. Let’s dive in.

Image 1 of 10

(Image credit: Intel)

Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

(Image credit: Intel)Image 1 of 10

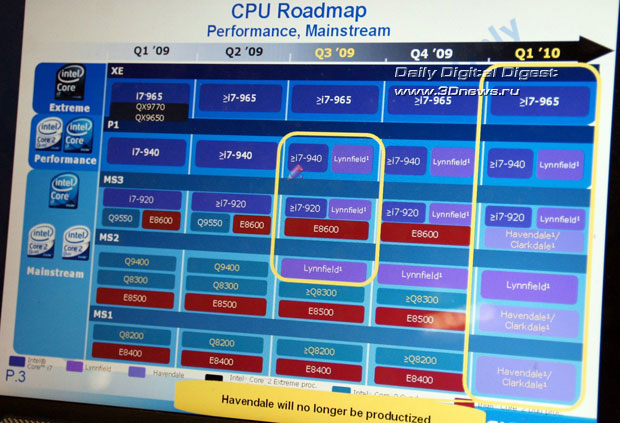

Intel Renames 10nm to 7nm

Before we get to the roadmaps, in a necessary move that will likely draw criticism, Intel is renaming its process nodes to align with the current naming conventions used by the third-party foundries like TSMC and Samsung.

This new policy begins with what was known as the 10nm Enhanced SuperFin process that is set to debut with the Alder Lake processors. Intel announced this process node long ago, and it is already in volume production.

Intel is rebranding the next 10nm node to ‘Intel 7’ and discarding the ‘nanometer’ nomenclature, so we won’t see the traditional ‘nm’ suffix attached to the company’s process nodes anymore. Instead, Intel will name its nodes based on performance, power, and area advances. As a result, all of Intel’s successive node names will be adjusted as well, with Intel’s 7nm becoming ‘Intel 4,’ and so on.

Intel’s shift in node naming comes as it builds out its own Intel Foundry Services (IFS) business, which will see it make chips for other companies as part of its IDM 2.0 initiative. Intel’s IFS will compete directly with TSMC and Samsung, and given that the node naming convention is already broken, aligning with the rest of the industry makes plenty of sense.

However, changing the 10nm Enhanced SuperFin naming while the ‘vanilla’ 10nm SuperFin is already shipping definitely isn’t as ideal as waiting for an entirely new node to make the change — this approach is unquestionably more confusing. In either case, Intel will eventually have to take criticism for making a change to its nomenclature at some point, and it has chosen to do so with its next line of chips. We’ll come back to expand on this topic a bit later in the article.

Intel Process Roadmap 2021 — 2025

Intel’s roadmap below starts with the 10nm SuperFin that currently ships in some of its products, like its Tiger Lake processors. However, as noted above, ‘Intel 7’ is the same 10nm Enhanced SuperFin process that Intel has already announced will power its Alder Lake and Sapphire Rapids chips — it just has a new name.

Similarly, Intel’s 7nm, which it recently announced will be delayed, is now branded as ‘Intel 4.’ The remaining two entries on the roadmap, ‘Intel 3’ and ‘Intel 20A’ represent what intel previously branded as 7+ and 5nm, respectively.

Image 1 of 5

(Image credit: Intel)

Image 1 of 5

(Image credit: Intel)Image 1 of 5

(Image credit: Intel)Image 1 of 5

(Image credit: Intel)Image 1 of 5

(Image credit: Intel)Image 1 of 5

Intel says that ‘Intel 7,’ the process formerly known as ’10nm Enhanced SuperFin,’ will ship this year for client (Alder Lake), and for the data center (Sapphire Rapids) in the first quarter of 2022. Intel says that ‘Intel 7’ delivers 10% to 15% more performance-per-watt than its predecessor, 10nm SuperFin.

As normal, that can translate to either higher peak performance (at the expense of efficiency) or increased efficiency (at the expense of performance), but you can’t have both simultaneously. It’s noteworthy that higher performance doesn’t scale linearly due to the increased power required at the upper end of the voltage/frequency curve, so Intel 7 likely won’t be 15% faster than 10nm SuperFin.

Moving on to newer climes, Intel 4 (previously known as 7nm) comes to market in products in the first half of 2023, though it will «be ready for production» in the second half of 2022. Intel says this node provides a 20% performance-per-watt gain over its predecessor (the same rules above apply) and represents the company’s full embrace of EUV technology. That’s an important step forward — Intel’s laggardly adoption of EUV fabrication is thought to be a major contributing factor to its 10nm delays.

Intel says this node provides a 20% performance-per-watt gain over its predecessor (the same rules above apply) and represents the company’s full embrace of EUV technology. That’s an important step forward — Intel’s laggardly adoption of EUV fabrication is thought to be a major contributing factor to its 10nm delays.

Chips based on the Intel 4 process will debut in 2023, with client Meteor Lake processors coming in the first half and Granite Rapids server products following. That timeline still leaves Intel’s competitors, like TSMC and Samsung, with a process node advantage in the 2023 time frame. TSMC projects it will be in full production of its 3nm node in 2023, explaining Intel’s continued need to outsource some products. Intel plans to leverage its packaging technology and disaggregated design philosophy to integrate externally-produced TSMC chips into its own products to help sidestep the delay.

Intel 3, previously branded as 7+, will bring an 18% performance-per-watt gain over Intel 4 when it shows up in products in the second half of 2023. ‘Intel 3’ is an incredibly fast follow to ‘Intel 4’ that launches earlier the same year, due to the previously mentioned delays. Still, Intel has confirmed that, based on its early modeling and test chip data, it represents «a higher level of improvement than a standard full node for Intel — or indeed for other vendors.»

‘Intel 3’ is an incredibly fast follow to ‘Intel 4’ that launches earlier the same year, due to the previously mentioned delays. Still, Intel has confirmed that, based on its early modeling and test chip data, it represents «a higher level of improvement than a standard full node for Intel — or indeed for other vendors.»

Intel plans to begin an entirely new era in the first half of 2024: The angstrom era. These chips represent the point where some physical features can no longer be accurately measured in nanometers, or billionths of a meter. Instead, these features will now be measured in angstroms, or one ten-billionth of a meter. The first angstrom-class process from Intel will come as 20A (A is for angstrom), which brings RibbonFET, Intel’s first gate-all-around (GAA) transistor, and PowerVia, a novel approach to delivering power to incredibly small transistors.

Intel Angstroms, RibbonFET and PowerVia

Image 1 of 7

Intel Process Roadmap 2021 — 2025 (Image credit: Intel)

Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

Process Roadmap (Image credit: Intel)Image 1 of 7

RibbonFET will mark Intel’s first gate-all-around (GAA) design and the company’s first new transistor design since FinFET debuted in 2011. Intel’s design features four stacked nanosheets, each surrounded entirely by a gate. Intel claims this design enables faster transistor switching while using the same drive current as multiple fins, but in a smaller area. This certainly seems plausible; Intel’s competitors have also adopted GAA designs.

Intel’s design features four stacked nanosheets, each surrounded entirely by a gate. Intel claims this design enables faster transistor switching while using the same drive current as multiple fins, but in a smaller area. This certainly seems plausible; Intel’s competitors have also adopted GAA designs.

Intel isn’t sharing much information about RibbonFET yet, but it bears a striking resemblance to IBM’s recently announced GAA/nanosheet tech that it fabbed on a 2nm test wafer (images below). This is incredibly relevant, as Intel recently announced in its IDM 2.0 announcement that it would collaborate with IBM on future logic and packaging technologies. This partnership is important for Intel as it looks to recover from years of stagnation with its process technologies. During our briefings with IBM about its research results, the company was quite clear that its new 2nm tech will benefit all of its partners, including Intel. You can read more about IBM’s similar tech here.

(Image credit: Intel)

As we noted in our coverage of IBM’s nanosheet/GAA tech, the smallest transistors in the world are of no use if you can’t wire them together, and that has been one of the most pressing constraints to shrinking to smaller nodes.

Intel’s new PowerVia technology seems to be a promising approach to navigating the problem with interconnects. PowerVia routes all power for the transistors directly to the transistors through the backside of the transistor. This essentially partitions power delivery to the backside of the transistors while data transmission interconnects remain in their traditional location on the other side.

Intel says that separating the power circuitry and the data-carrying interconnects improves voltage droop characteristics, allowing for faster transistor switching while enabling denser signal routing on the top of the chip. Signaling also benefits because the simplified routing enables the use of faster wires with reduced resistance and capacitance.

This technique will obviously pose many of its own challenges, such as the power delivery circuitry potentially serving as an insulating layer that traps heat within the transistors. It will be interesting to see how Intel tackles those potential pitfalls.

Intel 18A and High NA EUV

(Image credit: Intel)

Intel didn’t include it in the roadmap, but it already has its next-gen angstrom-class process in development. ‘Intel 18A’ is already planned for «early 2025» with enhancements to the RibbonFET transistors.

Intel’s 18A will be the inflection point for using High NA EUV, which is a new ultra-precise version of EUV machines that can etch designs at smaller (<8nm) resolutions than current machines. These machines will be required to do single-patterning EUV at such fine geometries, while existing EUV tools would require less-desirable multi-patterning EUV techniques.

Intel says it will be the first company to receive a High NA EUV machine from ASML, signaling that it plans to lead with the next-gen EUV machines as opposed to lagging behind TSMC as it did with 10nm. It’s noteworthy that while Intel did state that it would be first to receive a High NA EUV machine, it didn’t claim that it would be the first to enter high volume manufacturing with High NA EUV.

Intel tells us that it will offer the leading-edge Intel 3 and the following nodes, including 20A and 18A, to its foundry customers. That means we will likely see Intel stick with offering its prospective foundry customers trailing edge nodes for now — Intel 3 doesn’t enter production until the second half of 2023.

(Image credit: Intel)

Intel’s summary says that the company will achieve process performance parity with the industry leader, TSMC, in 2024, and take the lead in 2025. However, Intel’s footnote specifies that this is based on performance-per-watt, and not transistor performance or density.

It’s noteworthy this parity statement only applies to Intel’s process tech, and not its end products. The company still plans to still compete with «leadership products» from now until 2025 through a combination of new microarchitectures, packaging innovations that tie together various technologies in new and more efficient ways (more on that below), and also by outsourcing some of its highest-end chip designs for the first time in its history. Intel says it will release both consumer and data center «CPU leadership» chips with an as-yet unspecified TSMC node in 2023.

Intel says it will release both consumer and data center «CPU leadership» chips with an as-yet unspecified TSMC node in 2023.

Intel Packaging Update

Image 1 of 9

(Image credit: Intel)

Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

(Image credit: Intel)Image 1 of 9

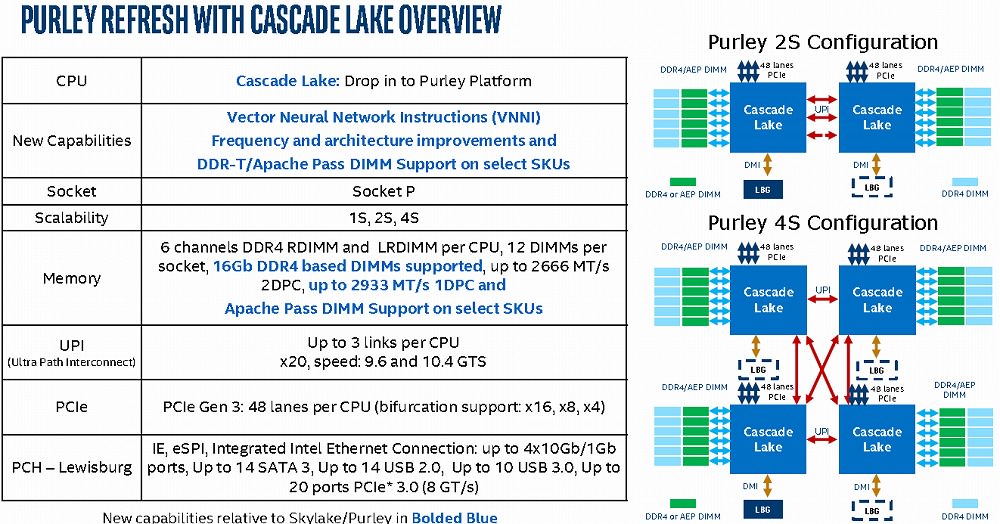

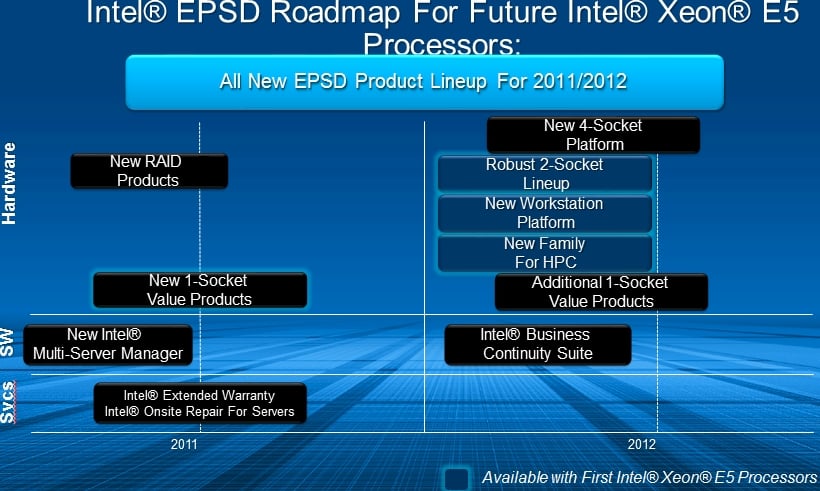

Intel’s packaging update was a bit more spartan. The company announced that it would use EMIB packaging tech, which uses an embedded silicon bridge in a package to connect multiple dies, for its Sapphire Rapids processors, marking the first data center product with the interconnect technology. This has been a bit of an open secret, as pictures of Sapphire Rapids have already surfaced. However, Intel did reveal that it will improve next-gen EMIB from a 55-micron bump pitch to 45 microns.

Intel’s Foveros 3D chip stacking technology debuted in the company’s Lakefield processors that the company recently retired, but the next-gen Foveros implementation debuts in Intel’s upcoming Meteor Lake processors. This generation of Foveros improves to a 36-micron bump pitch.

Intel’s upcoming Foveros Omni takes things a step further. This interconnect technology uses copper columns at the peripheries of the interconnected dies to deliver power, while TSV connections throughout the center of the die shuffle data between the chips. This differs from the first-gen Foveros because it separates the data and power transmission, allowing for cleaner routing for both power and data signals. In turn, this enables a tighter 25-micron bump pitch and allows mixing and matching different base dies. This technology is essentially the same as Intel’s ODI packaging tech, which you can read more about here.

Intel has also given its hybrid bonding tech a new use in conjunction with its Foveros packaging. Foveros Direct leverages die-on-wafer hybrid bonding (copper-to-copper) as an alternative to standard thermo-compression bonding. This new technique features aggressive sub-10nm bump pitches that increase interconnect density, simplify interconnect circuitry, and lower resistance and power consumption — all while serving up higher bandwidth. Intel has already taped out a stacked SRAM chip with hybrid bonding, and now the company is applying the technique to its Foveros interconnect. However, Intel hasn’t stated when this tech will come to market.

Foveros Direct leverages die-on-wafer hybrid bonding (copper-to-copper) as an alternative to standard thermo-compression bonding. This new technique features aggressive sub-10nm bump pitches that increase interconnect density, simplify interconnect circuitry, and lower resistance and power consumption — all while serving up higher bandwidth. Intel has already taped out a stacked SRAM chip with hybrid bonding, and now the company is applying the technique to its Foveros interconnect. However, Intel hasn’t stated when this tech will come to market.

Intel Renames Process Nodes — Continued

Image 1 of 2

(Image credit: Intel)

Image 1 of 2

(Image credit: Intel)Image 1 of 2

Intel’s decision to rename its process nodes will certainly garner plenty of criticism, but it is a necessary evil. Intel’s process node naming was simple enough back in 1997, when node naming was based on the transistor’s gate length (or M1 half-pitch metric), but the correlation between the physical measurement and the actual name of the node changed over time. In fact, the arrival of FinFET transistors killed the correlation between the two entirely. Now Intel’s node naming changes come with either new technology or increased transistor density.

In fact, the arrival of FinFET transistors killed the correlation between the two entirely. Now Intel’s node naming changes come with either new technology or increased transistor density.

When it comes to nanometers, everyone knows that a smaller number is better for semiconductors. But while Intel’s naming diverged from a physical measurement slowly, third-party foundries like TSMC and Samsung made more radical adjustments based on even simple changes to the underlying technology. That spurred name changes for situations like the move from planar to FinFET transistors, even when the transition didn’t improve transistor density. Even PDK/BKM (Product Design Kit/Best Known Method) changes are enough of an excuse for third-party fabs to assign a new number to a process, turning the naming convention into more of a marketing exercise than a metric tied to any sort of physical measurement.

And the third-party foundries are winning the marketing wars. However, in the real world, a plethora of factors influence the economics and performance of a process node, such as transistor density, peak performance, performance per watt, different types of logic/circuits, SRAM density, and so on.

Intel’s missteps with its 10nm node, which caused a string of ‘+’ revisions and the delay of three following nodes, exacerbated the node naming issue as Intel ceded its process leadership to TSMC. Now, depending on when TSMC first ships its 3nm process, the company leads Intel by either one or two process nodes. That’s particularly painful for Intel because while its process tech does lag TSMC, its naming lags, too, falsely amplifying the extent of TSMC’s lead. Currently, based on transistor density, Intel’s 10nm is more analogous to TSMC’s 7nm, and Intel’s 7nm is comparable to TSMC’s 5nm, so a naming adjustment makes sense.

Intel also shared some supporting quotes (in the album above) that point to others in the industry pointing out that node naming no longer has any correlation to the actual tech. (One of Intel’s supporting quotes in the slide above says Intel 7nm is close to TSMC 3nm, but take that with a grain of salt.)

It makes sense for Intel to move forward to new naming now that it will compete more directly with TSMC and Samsung in the foundry market, but we’re surprised that it chose to make the move at its 10nm generation instead of waiting for 7nm (which is now called Intel 4). Given that Intel has already shifted from its ‘+’ naming to using full names, like ‘Enhanced SuperFin,’ the new naming adds yet another layer of confusion to interpreting the company’s progress because it is applied to products that are already in flight. Let’s hope Intel sticks to this naming convention, and its roadmap, at least for a while.

Given that Intel has already shifted from its ‘+’ naming to using full names, like ‘Enhanced SuperFin,’ the new naming adds yet another layer of confusion to interpreting the company’s progress because it is applied to products that are already in flight. Let’s hope Intel sticks to this naming convention, and its roadmap, at least for a while.

Paul Alcorn is the Deputy Managing Editor for Tom’s Hardware US. He writes news and reviews on CPUs, storage and enterprise hardware.

Topics

CPUs

Tom’s Hardware is part of Future US Inc, an international media group and leading digital publisher. Visit our corporate site .

©

Future US, Inc. Full 7th Floor, 130 West 42nd Street,

New York,

NY 10036.

Intel has a new architecture roadmap and a plan to retake its chipmaking crown in 2025

Intel is rethinking how it releases — and brands — its semiconductor innovations, CEO Pat Gelsinger announced today at the company’s Intel Accelerated webcast. The announcement includes the broad strokes of the next half-decade of Intel’s processor roadmap, new chip and packaging technologies, and a promise of an “annual cadence of innovation,” with the ultimate goal of seeing Intel retake its leadership in the processor space by 2025.

The announcement includes the broad strokes of the next half-decade of Intel’s processor roadmap, new chip and packaging technologies, and a promise of an “annual cadence of innovation,” with the ultimate goal of seeing Intel retake its leadership in the processor space by 2025.

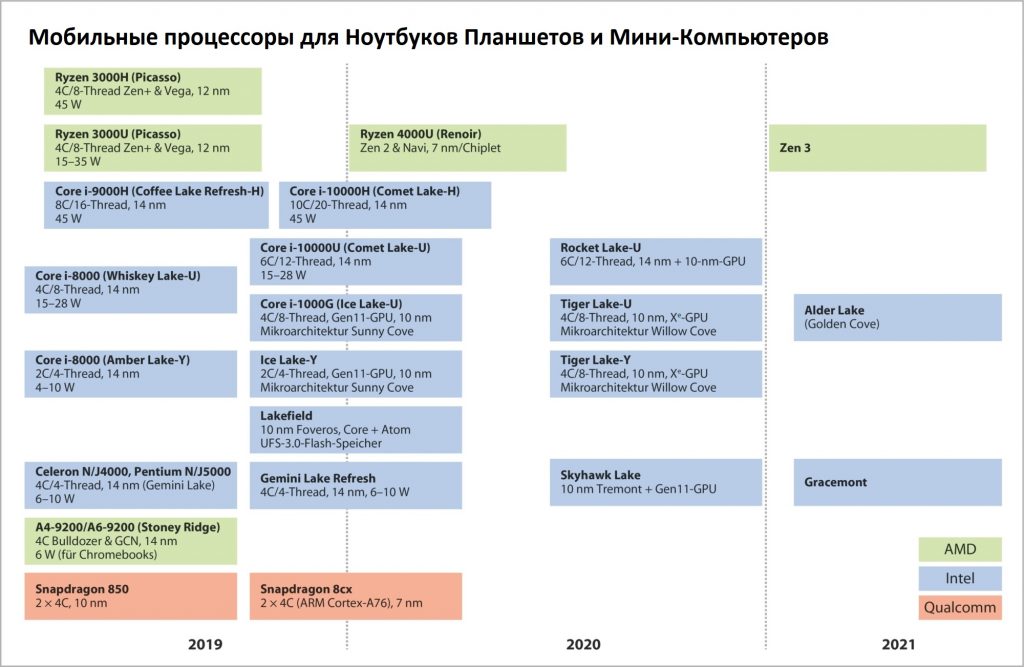

Future Intel products (starting as early as its upcoming 12th Gen Alder Lake chips later this year) will no longer use the nanometer-based node nomenclature that both it and the rest of the chipmaking industry has used for years. Instead, Intel is debuting a new naming scheme that it says will provide “a more accurate view of process nodes across the industry” and how Intel’s products fit into that landscape.

Intel rebrands its node naming

How that works in practice is that those new third-generation 10nm chips will be referred to as “Intel 7,” instead of getting some 10nm-based name (like last year’s 10nm SuperFin chips).

At first glance, it sounds a lot like a cheap marketing tactic designed to make Intel’s upcoming 10nm chips look more competitive next to products from AMD, which are already on TSMC’s 7nm node, or Apple’s 5nm M1 chips. And while that’s technically true, it’s not as unfair of a comparison as it necessarily looks. In modern semiconductors, node names don’t actually refer to the size of a transistor on a chip: thanks to advances like 3D packaging technologies and the physical realities of semiconductor design, that hasn’t been the case since 1997 (as noted by ExtremeTech).

And while that’s technically true, it’s not as unfair of a comparison as it necessarily looks. In modern semiconductors, node names don’t actually refer to the size of a transistor on a chip: thanks to advances like 3D packaging technologies and the physical realities of semiconductor design, that hasn’t been the case since 1997 (as noted by ExtremeTech).

And from a technical perspective, Intel’s 10nm chips are broadly on par with “7nm” branded hardware from competitors like TSMC or Samsung, using similar production technologies and offering comparable transistor density. That’s something that translates to commercial hardware, too: we’ve already seen that Intel’s current 10nm chips are still competitive with AMD’s cutting-edge 7nm Ryzen chips, for example.

All that is to say that Intel’s rebranding here isn’t entirely unfair to see, even if it does make it harder to parse when those bigger “node” change advances are happening with the new nomenclature.

Intel’s updated roadmap and node namingImage: Intel

Here’s a look at Intel’s new roadmap and what it all actually means.

• Intel 7 is the new name for what would have been Intel’s third-generation 10nm technology and the successor to Intel’s 10nm SuperFin (aka Intel’s second-generation 10nm chips, found most notably in its 11th Gen Tiger Lake chips). Intel says that the new Intel 7 hardware will offer approximately 10 percent to 15 percent improvements in performance-per-watt compared to the previous generation — or, as is always the case, improved power efficiency and battery life should hardware manufacturers prefer to keep performance the same.

The first Intel 7-based products will show up as early as this year, with the already previewed Alder Lake chips coming at the end of 2021 for consumer products, and the upcoming Sapphire Rapids chips in 2022 for data centers.

• Intel 4 is the architecture formally known as Intel’s 7nm process, which Intel infamously was forced to delay out to 2023 last summer following manufacturing issues. Originally planned for 2021, it’s the next major jump in technology for Intel, using EUV (extreme ultraviolet) technology — something already utilized by Samsung and TSMC’s 5nm node products, for comparison. It’ll still use the same broad FinFET transistor architecture that Intel’s been using since 2011. Thanks to all those improvements, Intel 4 is expected to feature a transistor density of about 200-250 million transistors per mm², compared to about 171.30 million transistors per mm² on TSMC’s current 5nm node.

Originally planned for 2021, it’s the next major jump in technology for Intel, using EUV (extreme ultraviolet) technology — something already utilized by Samsung and TSMC’s 5nm node products, for comparison. It’ll still use the same broad FinFET transistor architecture that Intel’s been using since 2011. Thanks to all those improvements, Intel 4 is expected to feature a transistor density of about 200-250 million transistors per mm², compared to about 171.30 million transistors per mm² on TSMC’s current 5nm node.

Intel says that Intel 4 will offer an approximately 20 percent jump in performance-per-watt while cutting down on overall area. Production is set for the second half of 2022, with the first Intel 4 products planned for 2023 (Meteor Lake for consumer products, and Granite Rapids for data center).

• Intel 3, set for manufacturing in the second half of 2023, is the new name for what would have been a second-generation 7nm product under Intel’s previous naming scheme. Like Intel 4, it’s still a FinFET product, although Intel says it’ll offer additional optimizations and use of EUV for roughly an 18 percent increase in performance-per-watt compared to Intel 4. No release date or product names for Intel 3 chips have been announced yet, but presumably, they won’t be available until 2024.

Like Intel 4, it’s still a FinFET product, although Intel says it’ll offer additional optimizations and use of EUV for roughly an 18 percent increase in performance-per-watt compared to Intel 4. No release date or product names for Intel 3 chips have been announced yet, but presumably, they won’t be available until 2024.

-

Intel 20A is the name for the next generation of Intel technologies that, under the old scheme, would have been the architecture following the formerly branded 7nm node. It’s also the most substantial announcement that Intel made today, technologically speaking, one that will see Intel debut its first new transistor architecture since FinFET in 2011, called “RibbonFET.” The new architecture will mark Intel’s first gate-all-around transistor, a fundamentally new transistor technology for the company that promises greater transistor density and smaller sizes. Additionally, 20A will see the introduction of “PowerVia,” a new technology that allows for wafers to be powered from the back of the chip, instead of requiring power to be rounded to the front.

A closer look at the coming updates for Intel 20A.Image: Intel

The “20A” in the title is meant to evoke the “Ångstrom era” of semiconductor design — an Ångstrom being a unit of measurement smaller than nanometer. (20Å = 2nm, although, like the other rebranded Intel names above, Intel 20A doesn’t refer to a specific measurement on the products themselves.)

Intel’s 20A isn’t expected to ramp until 2024, and, like Intel 3, it doesn’t have any formally announced release date or products yet.

- Intel 18A is the farthest in the future piece of Intel’s roadmap and will feature the second generation of Intel’s RibbotFET technology for “another major jump in transistor performance.” Intel says that Intel 18A is in development for “early 2025,” and that it expects this generation of technology to re-establish its semiconductor leadership.

In addition to all of its process roadmap news, Intel also announced two major updates to its Foveros chip-stacking packaging technologies (the second-generation of which is set to debut in Intel 4’s Meteor Lake in 2023. ) Foveros chip stacking combines several hardware elements into a single die, like Intel’s Lakefield chips, which pile together five CPU cores, an integrated GPU, and DRAM into a compact stack to save internal space compared to a traditional design.

) Foveros chip stacking combines several hardware elements into a single die, like Intel’s Lakefield chips, which pile together five CPU cores, an integrated GPU, and DRAM into a compact stack to save internal space compared to a traditional design.

Image: Intel

Foveros Omni will allow for more variety in stacked chips by making it easier to mix-and-match tiles, regardless of their specific size — for example, allowing for a base tile that’s smaller than the top tile in a stack. And Foveros Direct will allow for direct copper-to-copper bonding between components, reducing resistance and decreasing bump pitches. Both of the new Foveros technologies are planned for production in 2023.

Intel’s new names may help the company recontextualize its current and future products more accurately against its competition, but the fact remains that Intel is behind. Even accepting that the Intel 7 is on par with 7nm products from other foundries, those foundries are already past their 7nm chips and on to 5nm hardware. Which means that the companies that rely on those external foundries — like Apple, AMD, Nvidia, Qualcomm, and virtually every other major tech company — can still get chips that are more advanced than Intel’s best work. Apple’s superlative M1 Macs, for example, already use 5nm chips from TSMC — and handily outpace Intel’s comparable products. AMD is rumored to be working on 5nm Zen 4 processors for as early as 2022, too, which could offer similarly concerning competition for Intel from its already encroaching competitor.

Which means that the companies that rely on those external foundries — like Apple, AMD, Nvidia, Qualcomm, and virtually every other major tech company — can still get chips that are more advanced than Intel’s best work. Apple’s superlative M1 Macs, for example, already use 5nm chips from TSMC — and handily outpace Intel’s comparable products. AMD is rumored to be working on 5nm Zen 4 processors for as early as 2022, too, which could offer similarly concerning competition for Intel from its already encroaching competitor.

Even with the ambitious, annual cadence for its roadmap, Intel is playing from behind; it doesn’t expect to fully catch up to the rest of the industry until Intel 20A in 2024. And it doesn’t expect to reclaim leadership in the semiconductor business until 2025 with Intel 18A. And all that assumes that Intel doesn’t hit any more delays or manufacturing snags like the ones that held up both its 10nm and 7nm processes (which arguably put the company in its current situation in the first place).

After years of setbacks, though, it’s clear that the revitalized Intel isn’t going down without a fight. But the next few years will see whether its efforts are enough.

Intel’s Layout & Process Roadmap to 2025 and Beyond — CNXSoft — Android Set-Top & Embedded News always strictly adheres to its own production schedules for new processes, in particular, its 10nm process suffers from many years of delays.

But the other day, an American company held an event that presented a process roadmap for the period up to 2025 and beyond, which includes 7nm, 4nm, 3nm, and even switching the Angstrom scale (1A = 0.1 nm) with process 20A expected in 2024/2025.

Intel’s Process Roadmap to 2025 and Beyond

Intel’s Historical and Future Processes

As for process nodes, here’s what to expect over the next few years:

- 10-15% and will be featured in Alder Lake for the customer in 2021 and Sapphire Rapids for the data center, with the latter expected to go into production in the first quarter of 2022.

- The Intel 4 promises a 20% increase in performance per watt over Intel 7 and is the first Intel FinFET node to use deep ultraviolet (EUV) lithography, which includes «a highly sophisticated lens and mirror optical system focusing a wavelength of 13 .5 nm for printing incredibly fine details on silicon.” The Intel 4 will be ready for production in H2 2022 with products shipping in 2023, including Meteor Lake for the customer and Granite Rapids for the data center.

- The Intel 3 is expected to provide an 18% increase in performance per watt over Intel 4 and the company will be ready to start manufacturing products based on this technology node in the second half of 2023. Intel has not yet announced which processor families will benefit from the new technology node.

- Intel 20A Coming in 2024 with RibbonFET and PowerVia technologies. RibbonFET is a transistor with universal gate that provides faster switching speeds of

transistors while providing faster switching speeds in a smaller footprint than FinFETs due to its multi-nanochannel structure. PowerVia is the implementation of power delivery on the back of the silicon die, eliminating the need for power routing on the front of the wafer.

PowerVia is the implementation of power delivery on the back of the silicon die, eliminating the need for power routing on the front of the wafer. - The Intel 18A is already in development with RibbonFET improvements that will provide another «major leap» in transistor performance in 2025.

Note that there seems to have been a marketing team involved here as Intel 7 used to be called «10nm Enhanced SuperFin» and Intel 4 used to be called «Intel 7nm» technology node. We guess it depends on how you measure it, and Intel has explained in the past that competitors have a different way of measuring transistor size.

Intel

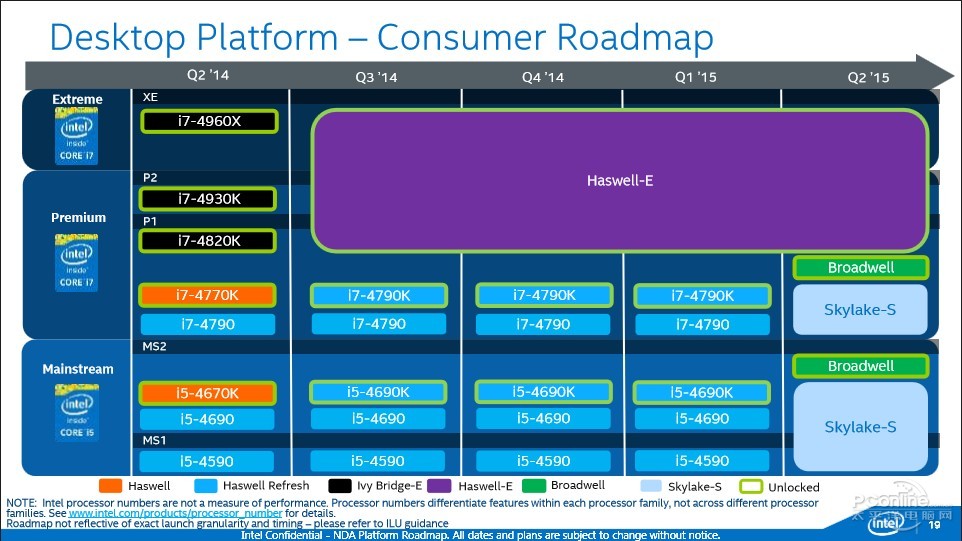

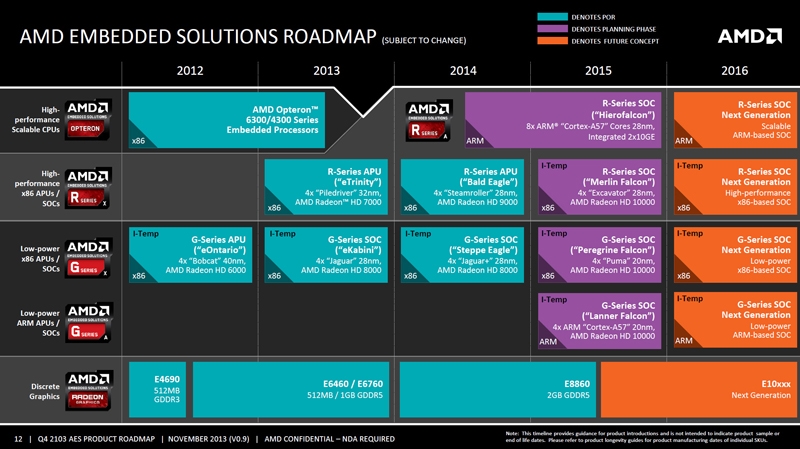

Chassis Innovations Intel also talked about chassis innovations such as the existing Foveros 3D stacking technology found in its ready-to-release Lakefield processors: