EPYC 7601 — AMD — WikiChip

From WikiChip

EPYC 7601 — AMD

< amd | epyc

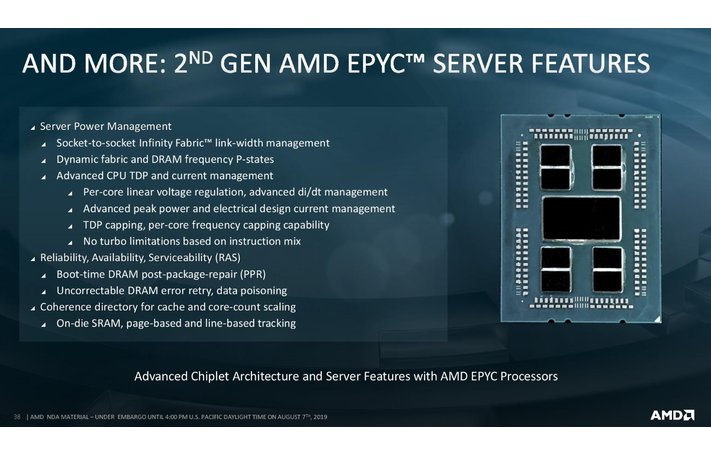

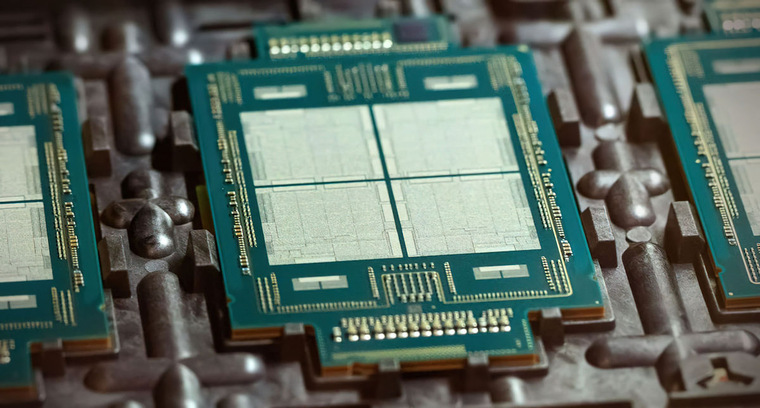

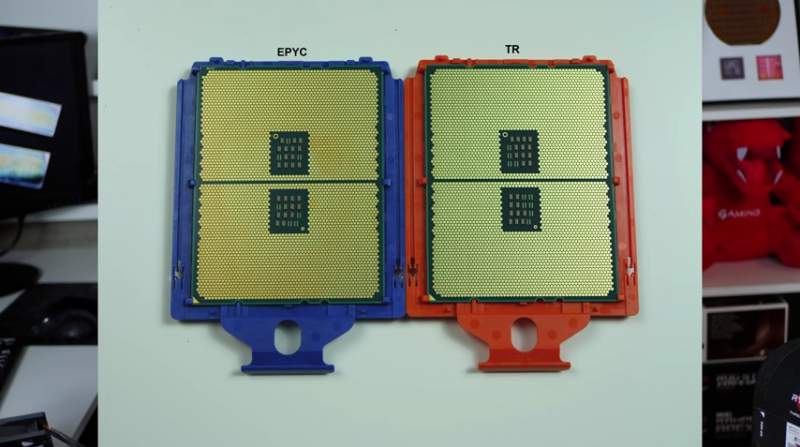

EPYC 7601 is a dual-socket 64-bit 32-core x86 enterprise server microprocessor introduced by AMD in mid-2017. This processor is based on the Zen microarchitecture and is manufactured on a 14 nm process. The 7601 has a base frequency of 2.2 GHz with a turbo frequency of 3.2 GHz for up to 12 active cores. This chip has a TDP of 180 W and supports up to 2 TiB of octa-channel DDR4-2666 ECC memory per socket.

| Preliminary Data! Information presented in this article deal with a microprocessor or chip that was recently announced or leaked, thus missing information regarding its features and exact specification. Information may be incomplete and can change by final release. |

Contents

- 1 Cache

- 2 Memory controller

- 3 Expansions

- 4 Features

- 5 Benchmarks

- Main article: Zen § Cache

[Edit/Modify Cache Info]

|

Cache Organization Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

[Edit/Modify Memory Info]

|

Integrated Memory Controller |

||||||||||||||

|

||||||||||||||

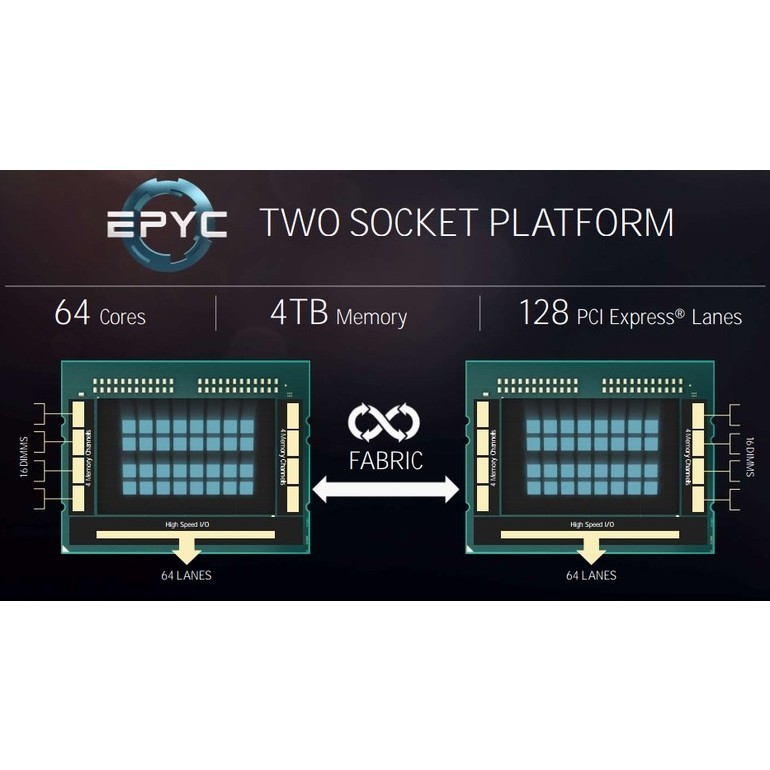

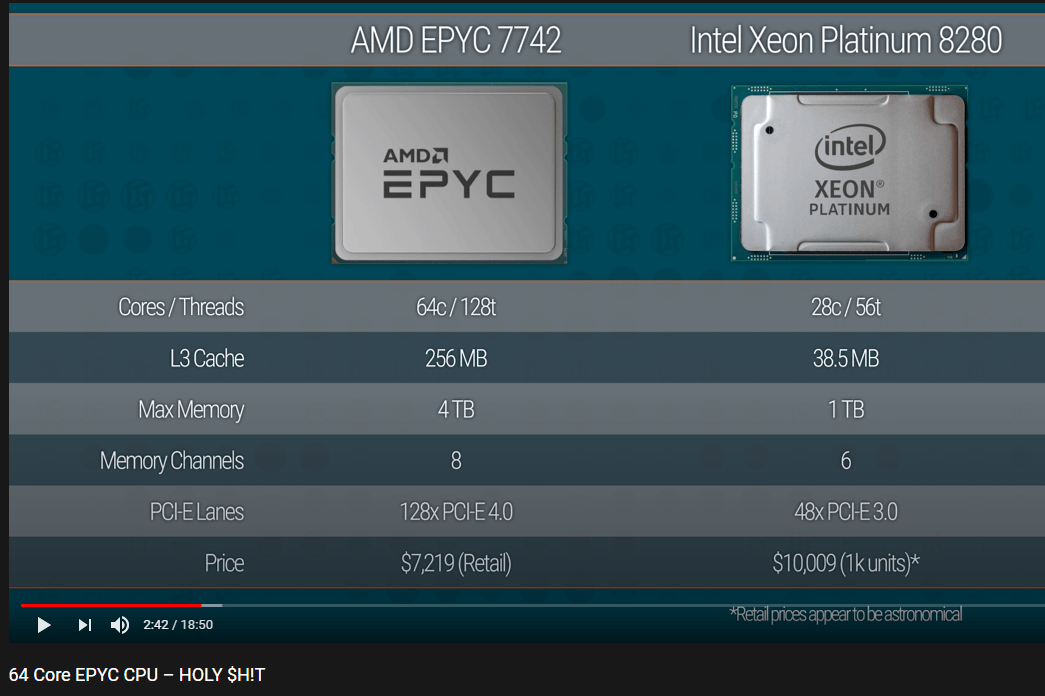

In a dual-socket configuration, the maximum supported memory doubles to 4 TiB along with the maximum theoretical bandwidth of 317. 9 GiB/s.

9 GiB/s.

Expansions[edit]

The EPYC 7601 has 128 Gen 3 PCIe lanes. In a dual-socket configuration, half of the lanes are used for inter-processor communication, so again 128 lanes are available for expansions.

[Edit/Modify Expansions Info]

|

Expansion Options |

||||||||

|

||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

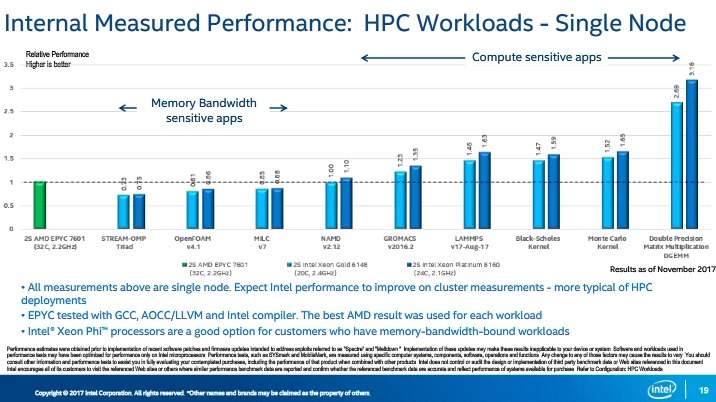

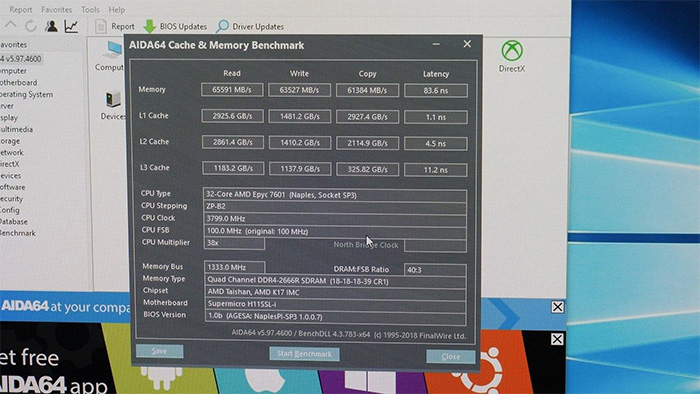

Benchmarks[edit]

[Edit Benchmarks]

Test:SPEC CPU2017

Tested:2017-10-24 18:28:59-0400

Chips: 2, Cores: 64, Copies: 128

Vendor: HPE

System: ProLiant DL385 Gen10 (2. 20 GHz, AMD EPYC 7601)

20 GHz, AMD EPYC 7601)

SPECrate2017_int_base: 271

SPECrate2017_int_peak: 299

Test:SPEC CPU2017

Tested:2017-10-25 06:03:04-0400

Chips: 2, Cores: 64, Copies: 128

Vendor: HPE

System: ProLiant DL385 Gen10 (2.20 GHz, AMD EPYC 7601)

SPECrate2017_fp_base: 257

SPECrate2017_fp_peak: 270

Facts about «EPYC 7601 — AMD»

RDF feed

| Has subobject

«Has subobject» is a predefined property representing a container construct and is provided by Semantic MediaWiki. |

EPYC 7601 — AMD#package +, EPYC 7601 — AMD#io +, EPYC 7601 — AMD + and EPYC 7601 — AMD + |

| base frequency | 2,200 MHz (2.2 GHz, 2,200,000 kHz) + |

| clock multiplier | 22 + |

| core count | 32 + |

| core family | 23 + |

| core model | 1 + |

| core name | Naples + |

| core stepping | B2 + |

| designer | AMD + |

| die area | 213 mm² (0. 33 in², 2.13 cm², 213,000,000 µm²) + 33 in², 2.13 cm², 213,000,000 µm²) + |

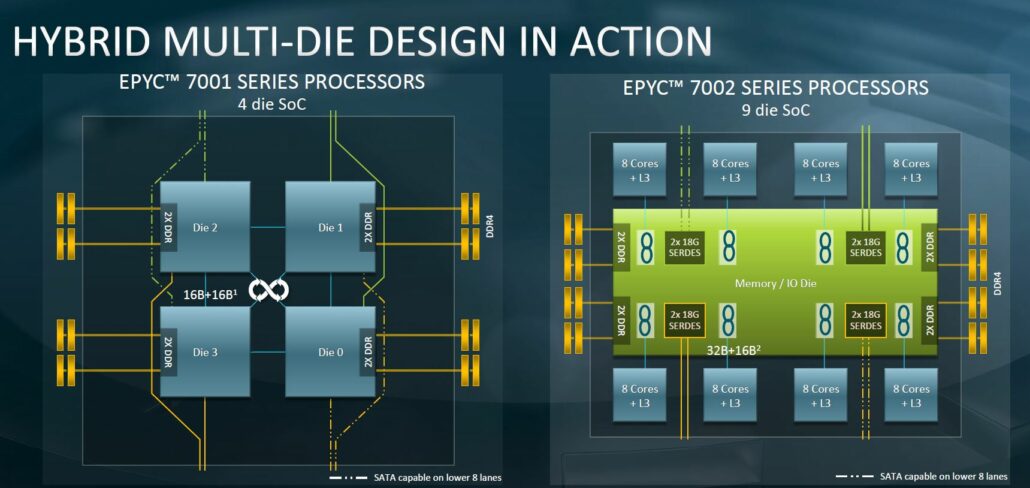

| die count | 4 + |

| family | EPYC + |

| first announced | June 20, 2017 + |

| first launched | June 20, 2017 + |

| full page name | amd/epyc/7601 + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has amd amd-v technology | true + |

| has amd amd-vi technology | true + |

| has amd secure encrypted virtualization technology | true + |

| has amd secure memory encryption technology | true + |

| has amd sensemi technology | true + |

| has amd transparent secure memory encryption technology | true + |

| has ecc memory support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension + and SenseMI Technology + |

| has locked clock multiplier | false + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| is multi-chip package | true + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 3 MiB (3,072 KiB, 3,145,728 B, 0. 00293 GiB) + 00293 GiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 16 MiB (16,384 KiB, 16,777,216 B, 0.0156 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 64 MiB (65,536 KiB, 67,108,864 B, 0.0625 GiB) + |

| ldate | June 20, 2017 + |

| manufacturer | GlobalFoundries + |

| market segment | Server + |

| max case temperature | 354.15 K (81 °C, 177.8 °F, 637.47 °R) + |

| max cpu count | 2 + |

| max memory | 2,097,152 MiB (2,147,483,648 KiB, 2,199,023,255,552 B, 2,048 GiB, 2 TiB) + |

| max memory bandwidth | 158. 95 GiB/s (276.573 GB/s, 162,764.8 MiB/s, 0.155 TiB/s, 0.171 TB/s) + 95 GiB/s (276.573 GB/s, 162,764.8 MiB/s, 0.155 TiB/s, 0.171 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 128 + |

| microarchitecture | Zen + |

| min case temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| model number | 7601 + |

| name | EPYC 7601 + |

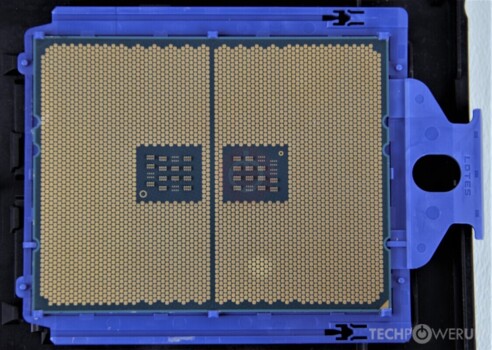

| package | FCLGA-4094 + |

| part number | PS7601BDVIHAF + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| release price | $ 4,200.00 (€ 3,780.00, £ 3,402.00, ¥ 433,986.00) + |

| series | 7000 + |

| smp max ways | 2 + |

| socket | Socket SP3 + |

| supported memory type | DDR4-2666 + |

| tdp | 180 W (180,000 mW, 0.241 hp, 0.18 kW) + |

| technology | CMOS + |

| thread count | 64 + |

| transistor count | 19,200,000,000 + |

| turbo frequency (10 cores) | 3,200 MHz (3. 2 GHz, 3,200,000 kHz) + 2 GHz, 3,200,000 kHz) + |

| turbo frequency (11 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (12 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (13 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (14 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (15 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (16 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (17 cores) | 2,700 MHz + |

| turbo frequency (18 cores) | 2,700 MHz + |

| turbo frequency (19 cores) | 2,700 MHz + |

| turbo frequency (1 core) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (20 cores) | 2,700 MHz + |

| turbo frequency (21 cores) | 2,700 MHz + |

| turbo frequency (22 cores) | 2,700 MHz + |

| turbo frequency (23 cores) | 2,700 MHz + |

| turbo frequency (24 cores) | 2,700 MHz + |

| turbo frequency (25 cores) | 2,700 MHz + |

| turbo frequency (26 cores) | 2,700 MHz + |

| turbo frequency (27 cores) | 2,700 MHz + |

| turbo frequency (28 cores) | 2,700 MHz + |

| turbo frequency (29 cores) | 2,700 MHz + |

| turbo frequency (2 cores) | 3,200 MHz (3. 2 GHz, 3,200,000 kHz) + 2 GHz, 3,200,000 kHz) + |

| turbo frequency (30 cores) | 2,700 MHz + |

| turbo frequency (31 cores) | 2,700 MHz + |

| turbo frequency (32 cores) | 2,700 MHz + |

| turbo frequency (3 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (4 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (5 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (6 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (7 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (8 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (9 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |

EPYC 7601 — AMD — WikiChip

From WikiChip

EPYC 7601 — AMD

< amd | epyc

EPYC 7601 is a dual-socket 64-bit 32-core x86 enterprise server microprocessor introduced by AMD in mid-2017. This processor is based on the Zen microarchitecture and is manufactured on a 14 nm process. The 7601 has a base frequency of 2.2 GHz with a turbo frequency of 3.2 GHz for up to 12 active cores. This chip has a TDP of 180 W and supports up to 2 TiB of octa-channel DDR4-2666 ECC memory per socket.

This processor is based on the Zen microarchitecture and is manufactured on a 14 nm process. The 7601 has a base frequency of 2.2 GHz with a turbo frequency of 3.2 GHz for up to 12 active cores. This chip has a TDP of 180 W and supports up to 2 TiB of octa-channel DDR4-2666 ECC memory per socket.

| Preliminary Data! Information presented in this article deal with a microprocessor or chip that was recently announced or leaked, thus missing information regarding its features and exact specification. Information may be incomplete and can change by final release. |

Contents

- 1 Cache

- 2 Memory controller

- 3 Expansions

- 4 Features

- 5 Benchmarks

- Main article: Zen § Cache

[Edit/Modify Cache Info]

|

Cache Organization Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

[Edit/Modify Memory Info]

|

Integrated Memory Controller |

||||||||||||||

|

||||||||||||||

In a dual-socket configuration, the maximum supported memory doubles to 4 TiB along with the maximum theoretical bandwidth of 317. 9 GiB/s.

9 GiB/s.

Expansions[edit]

The EPYC 7601 has 128 Gen 3 PCIe lanes. In a dual-socket configuration, half of the lanes are used for inter-processor communication, so again 128 lanes are available for expansions.

[Edit/Modify Expansions Info]

|

Expansion Options |

||||||||

|

||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Benchmarks[edit]

[Edit Benchmarks]

Test:SPEC CPU2017

Tested:2017-10-24 18:28:59-0400

Chips: 2, Cores: 64, Copies: 128

Vendor: HPE

System: ProLiant DL385 Gen10 (2. 20 GHz, AMD EPYC 7601)

20 GHz, AMD EPYC 7601)

SPECrate2017_int_base: 271

SPECrate2017_int_peak: 299

Test:SPEC CPU2017

Tested:2017-10-25 06:03:04-0400

Chips: 2, Cores: 64, Copies: 128

Vendor: HPE

System: ProLiant DL385 Gen10 (2.20 GHz, AMD EPYC 7601)

SPECrate2017_fp_base: 257

SPECrate2017_fp_peak: 270

Facts about «EPYC 7601 — AMD»

RDF feed

| Has subobject

«Has subobject» is a predefined property representing a container construct and is provided by Semantic MediaWiki. |

EPYC 7601 — AMD#package +, EPYC 7601 — AMD#io +, EPYC 7601 — AMD + and EPYC 7601 — AMD + |

| base frequency | 2,200 MHz (2.2 GHz, 2,200,000 kHz) + |

| clock multiplier | 22 + |

| core count | 32 + |

| core family | 23 + |

| core model | 1 + |

| core name | Naples + |

| core stepping | B2 + |

| designer | AMD + |

| die area | 213 mm² (0. 33 in², 2.13 cm², 213,000,000 µm²) + 33 in², 2.13 cm², 213,000,000 µm²) + |

| die count | 4 + |

| family | EPYC + |

| first announced | June 20, 2017 + |

| first launched | June 20, 2017 + |

| full page name | amd/epyc/7601 + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has amd amd-v technology | true + |

| has amd amd-vi technology | true + |

| has amd secure encrypted virtualization technology | true + |

| has amd secure memory encryption technology | true + |

| has amd sensemi technology | true + |

| has amd transparent secure memory encryption technology | true + |

| has ecc memory support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension + and SenseMI Technology + |

| has locked clock multiplier | false + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| is multi-chip package | true + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 3 MiB (3,072 KiB, 3,145,728 B, 0. 00293 GiB) + 00293 GiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 16 MiB (16,384 KiB, 16,777,216 B, 0.0156 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 64 MiB (65,536 KiB, 67,108,864 B, 0.0625 GiB) + |

| ldate | June 20, 2017 + |

| manufacturer | GlobalFoundries + |

| market segment | Server + |

| max case temperature | 354.15 K (81 °C, 177.8 °F, 637.47 °R) + |

| max cpu count | 2 + |

| max memory | 2,097,152 MiB (2,147,483,648 KiB, 2,199,023,255,552 B, 2,048 GiB, 2 TiB) + |

| max memory bandwidth | 158. 95 GiB/s (276.573 GB/s, 162,764.8 MiB/s, 0.155 TiB/s, 0.171 TB/s) + 95 GiB/s (276.573 GB/s, 162,764.8 MiB/s, 0.155 TiB/s, 0.171 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 128 + |

| microarchitecture | Zen + |

| min case temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| model number | 7601 + |

| name | EPYC 7601 + |

| package | FCLGA-4094 + |

| part number | PS7601BDVIHAF + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| release price | $ 4,200.00 (€ 3,780.00, £ 3,402.00, ¥ 433,986.00) + |

| series | 7000 + |

| smp max ways | 2 + |

| socket | Socket SP3 + |

| supported memory type | DDR4-2666 + |

| tdp | 180 W (180,000 mW, 0.241 hp, 0.18 kW) + |

| technology | CMOS + |

| thread count | 64 + |

| transistor count | 19,200,000,000 + |

| turbo frequency (10 cores) | 3,200 MHz (3. 2 GHz, 3,200,000 kHz) + 2 GHz, 3,200,000 kHz) + |

| turbo frequency (11 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (12 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (13 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (14 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (15 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (16 cores) | 2,700 MHz (2.7 GHz, 2,700,000 kHz) + |

| turbo frequency (17 cores) | 2,700 MHz + |

| turbo frequency (18 cores) | 2,700 MHz + |

| turbo frequency (19 cores) | 2,700 MHz + |

| turbo frequency (1 core) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (20 cores) | 2,700 MHz + |

| turbo frequency (21 cores) | 2,700 MHz + |

| turbo frequency (22 cores) | 2,700 MHz + |

| turbo frequency (23 cores) | 2,700 MHz + |

| turbo frequency (24 cores) | 2,700 MHz + |

| turbo frequency (25 cores) | 2,700 MHz + |

| turbo frequency (26 cores) | 2,700 MHz + |

| turbo frequency (27 cores) | 2,700 MHz + |

| turbo frequency (28 cores) | 2,700 MHz + |

| turbo frequency (29 cores) | 2,700 MHz + |

| turbo frequency (2 cores) | 3,200 MHz (3. 2 GHz, 3,200,000 kHz) + 2 GHz, 3,200,000 kHz) + |

| turbo frequency (30 cores) | 2,700 MHz + |

| turbo frequency (31 cores) | 2,700 MHz + |

| turbo frequency (32 cores) | 2,700 MHz + |

| turbo frequency (3 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (4 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (5 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (6 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (7 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (8 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| turbo frequency (9 cores) | 3,200 MHz (3.2 GHz, 3,200,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |

AMD EPYC 7601 processor review: specifications, benchmark tests

The EPYC 7601 processor was released by AMD, release date: June 2017. The processor is designed for server computers and is built on the Zen architecture.

The processor is designed for server computers and is built on the Zen architecture.

Processor unlocked for overclocking. The total number of cores is 32, threads are 64. The maximum clock speed of the processor is 3.2 GHz. Technological process — 14 nm. Cache size: L1 — 96 KB (per core), L2 — 512 KB (per core), L3 — 64 MB.

Supported memory type: DDR4.

Supported socket type: TR4. The maximum number of processors in the configuration is 2. Power consumption (TDP): 180 Watt.

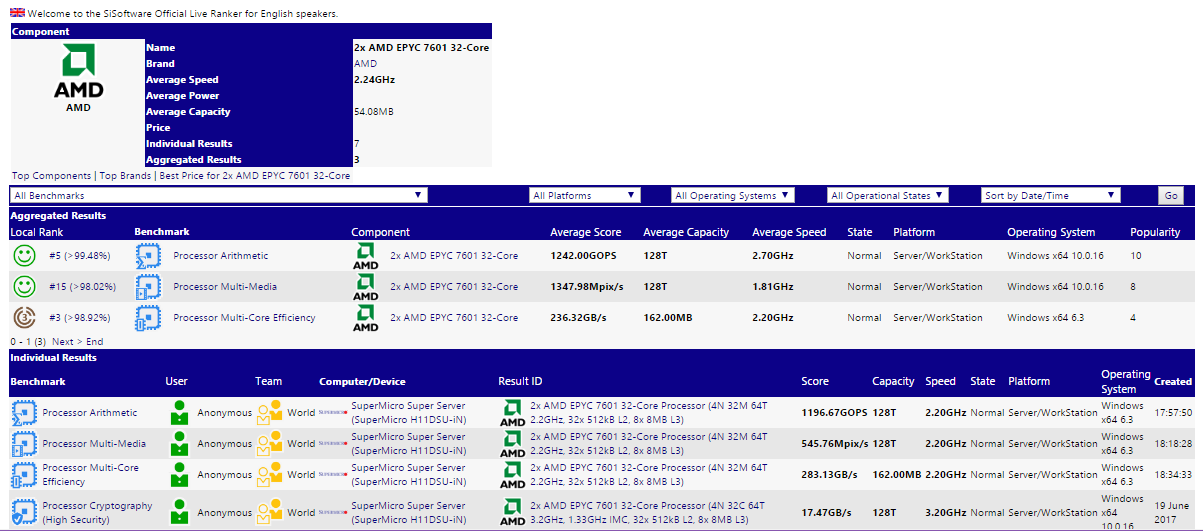

Benchmarks

| PassMark Single thread mark |

|

||||

| PassMark CPU mark |

|

|

| Title | Meaning |

|---|---|

| PassMark — Single thread mark | 1841 |

| PassMark — CPU mark | 56414 |

Features

| Architecture name | Zen |

| Family | AMD EPYC |

| Production date | June 2017 |

| Place in the ranking | 388 |

| Series | AMD EPYC 7000 Series |

| Applicability | Server |

| Support 64 bit | |

| Base frequency | 2. 2 GHz 2 GHz |

| Crystal area | 192mm |

| Level 1 cache | 96 KB (per core) |

| Level 2 cache | 512 KB (per core) |

| Level 3 cache | 64MB |

| Process | 14 nm |

| Maximum frequency | 3.2 GHz |

| Number of cores | 32 |

| Number of threads | 64 |

| Number of transistors | 4800 million |

| Unlocked | |

| Maximum number of memory channels | 8 |

| Maximum memory bandwidth | 341 GB/s |

| Supported memory frequency | 2666 MHz |

| Supported memory types | DDR4 |

| Maximum number of processors in configuration | 2 |

| Socket Count | 1P/2P |

| Supported sockets | TR4 |

| Power consumption (TDP) | 180 Watt |

| PCI Express revision | x128 |

| AMD Virtualization (AMD-V™) | |

0625 GiB

0625 GiB  1

1

0625 GiB

0625 GiB  1

1

This parameter is higher than 93% of products

This parameter is higher than 93% of products  3 MB

3 MB